Na eletrônica, um circuito de amostra e retenção (S&H) é um dispositivo analógico usado para tirar a tensão de um sinal analógico em constante mudança e bloqueia seu valor em um nível estável por um período mínimo de tempo específico. Esses circuitos são os dispositivos básicos de memória analógica. Eles são normalmente usados em ADC (conversores analógico-digital) para eliminar as diferenças no sinal de entrada que podem danificar o processo de mudança. Um circuito típico de amostra e retenção armazena carga elétrica em um capacitor e mantém pelo menos um dispositivo de comutação como um transistor de efeito de campo mudar e geralmente um op-amp (amplificador operacional) .

Para amostrar o sinal i / p, a chave une o capacitor ao o / p de um amplificador de buffer. Esta amplificador amplifica o capacitor de forma que a tensão através do capacitor seja quase igual ou proporcional à tensão de entrada. Na forma de espera, a chave separa o capacitor do buffer. O capacitor é sempre descarregado por suas próprias correntes de saída e correntes de carga úteis, o que torna o circuito essencialmente instável, mas a queda de tensão em um determinado tempo de espera permanece dentro de uma margem de erro adequada.

O que é Sample and Hold Circuit?

O circuito de amostra e retenção é um circuito eletronico o que torna os exemplos de voltagem dados a ele como informação, e desse ponto em diante, ele guarda essas amostras pelo tempo positivo. O tempo entre o qual o circuito de amostra e retenção produz a amostra do sinal i / p é chamado de tempo de amostragem. Correspondentemente, o tempo de duração do circuito em que ele mantém o valor amostrado é chamado de tempo de retenção.

Circuito de amostra e retenção

Geralmente, o tempo de amostragem é entre 1 µs-14 µs, enquanto o tempo de espera pode esperar qualquer valor conforme necessário na aplicação. Não será errado afirmar que o capacitor é o núcleo do circuito de amostra e retenção. Isso ocorre porque o capacitor exibido nele carrega até seu valor de pico quando a chave é aberta, ou seja, durante a amostragem e mantém a tensão inspecionada quando a chave é fechada.

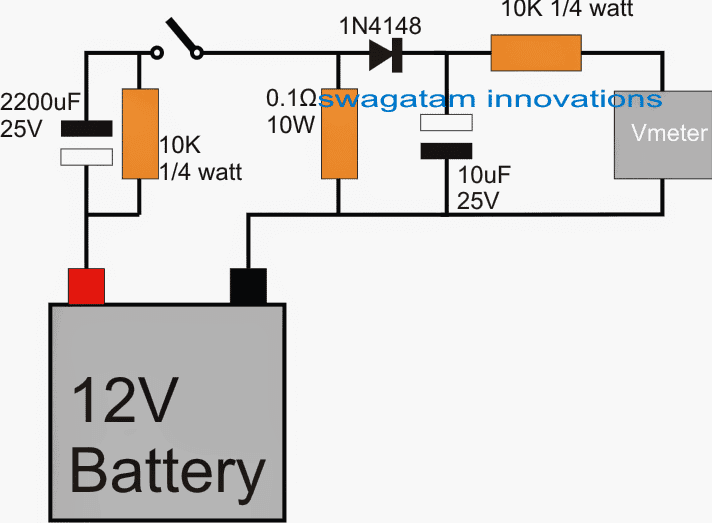

Diagrama de circuito de amostra e retenção

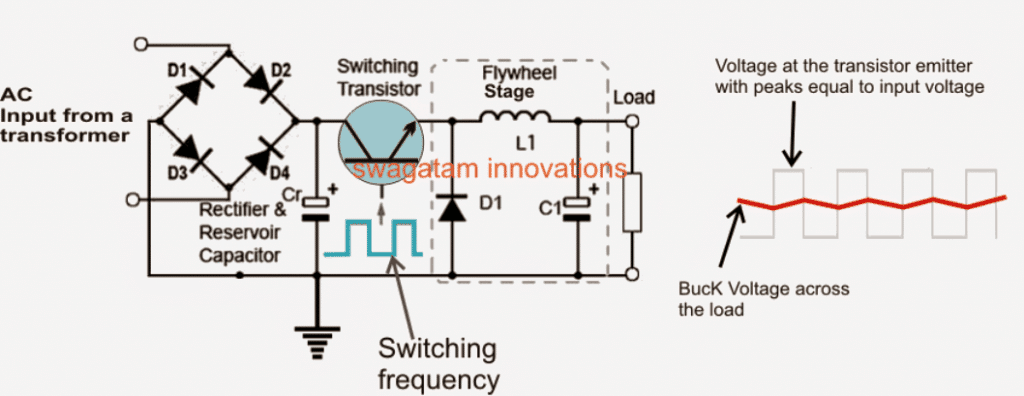

O diagrama de circuito abaixo mostra o circuito de amostra e retenção com a ajuda de um Op-Amp. Está claro no diagrama de circuito que dois amplificadores operacionais estão ligados por meio de um switch. Quando a chave está travada, o método de amostragem aparecerá na imagem e quando a chave estiver destravada, o resultado da retenção estará lá. O capacitor aliado ao segundo amplificador operacional nada mais é do que um capacitor de retenção.

Circuito de amostra e retenção

Usando este circuito de amostra e retenção, podemos obter amostras do sinal analógico, seguido por um capacitor. Ele contém essas amostras por um determinado período. Como resultado disso, um sinal estável é produzido e pode ser alterado para o sinal digital com a ajuda de ADC (conversores analógico para digital) .

Trabalho de circuito de amostra e retenção

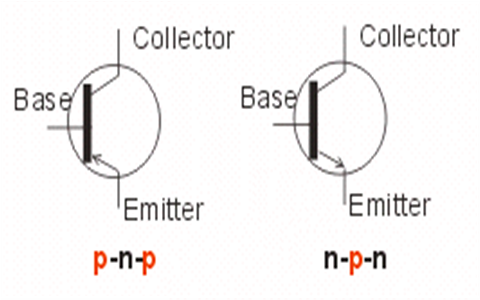

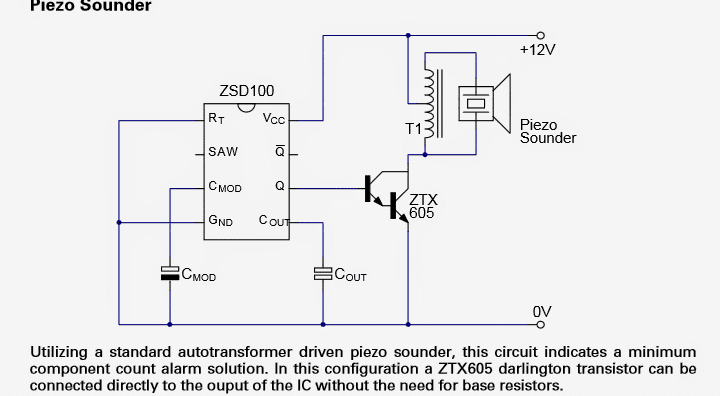

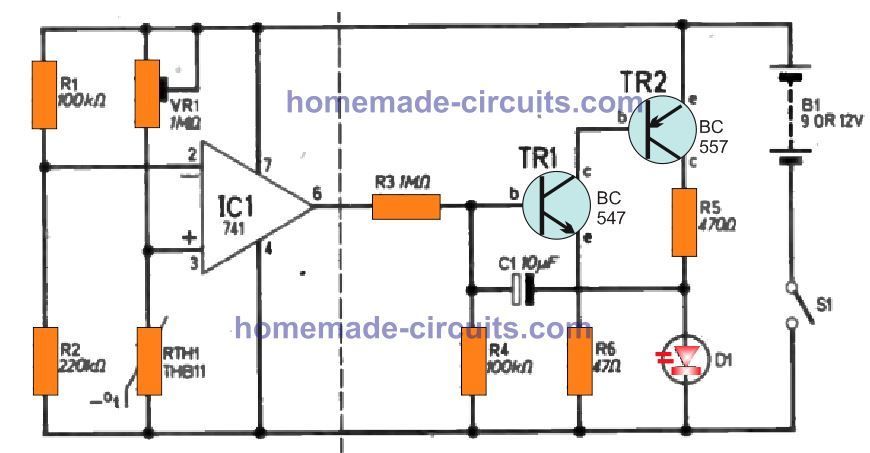

O funcionamento deste circuito pode ser entendido simplesmente usando seus componentes funcionando. Os principais componentes para construir o circuito de amostra e retenção incluem um MOSFET tipo Enhancement de canal N, um capacitor e um amplificador operacional de alta precisão.

Como um elemento de comutação, o MOSFET de aprimoramento de canal N é usado. A tensão de entrada é fornecida por meio de seu terminal de dreno e a tensão de controle também é fornecida por meio de seu terminal de porta. Quando o pulso + ve da tensão de controle é aplicado, o MOSFET será o estado ativado. E funciona como um interruptor fechado. Por outro lado, quando a tensão de controle é zero, o MOSFET será desativado e funcionará como a chave aberta.

Circuito de amostra e retenção usando Op-Amp

Quando o MOSFET funciona como uma chave fechada, o sinal analógico fornecido a ele através do terminal de drenagem será alimentado para o capacitor. Então, o capacitor carregará até seu valor de pico. Quando a chave é liberada, o capacitor interrompe o carregamento. Devido ao amplificador operacional de alta impedância conectado na extremidade do circuito, o capacitor conhecerá alta impedância, devido a isso, ele não pode ser descarregado

Isso direciona para a retenção da carga pelo capacitor pela quantidade exata de tempo. Isso pode ser referido como período de espera. E o tempo no qual as amostras de tensão i / p são produzidas é denominado período de amostragem. O o / p processado pelo op-amp durante todo o período de espera. Portanto, o período de espera tem implicações para os Op-Amps.

Formas de onda de entrada e saída

As formas de onda do circuito de amostra e retenção conforme explicado no diagrama a seguir. É claro pela forma de onda do circuito, que durante o período ON qual será a tensão em o / p. Durante o período OFF, a tensão que existe na o / p do op-amp.

Formas de onda de entrada e saída

Aplicativos de circuito de amostra e retenção

As aplicações do circuito de amostra e retenção incluem o seguinte

- Osciloscópios de amostragem

- Sistema de Distribuição de Dados

- Voltímetros Digitais

- Processamento de Sinal Analógico

- Filtros de construção de sinal

- Sistema de conversão de dados

Portanto, tudo se resume ao circuito de amostragem e retenção. Em termos simples, este circuito produz as amostras do sinal analógico i / p e mantém os valores de amostragem mais recentes para o tempo exato e os replica em o / p. Esperamos que você tenha entendido melhor este conceito. Além disso, qualquer dúvida sobre este conceito ou para implementar qualquer projeto elétrico, por favor, dê seu feedback comentando na seção de comentários abaixo. Aqui está uma pergunta para você, qual é a função do circuito de amostra e retenção?

![Circuitos do carregador de bateria de 12V [usando LM317, LM338, L200, transistores]](https://electronics.jf-parede.pt/img/battery-chargers/11/12v-battery-charger-circuits-using-lm317.png)