A principal desvantagem do circuito combinacional ou seja, ele não usa nenhuma memória para salvar os estados presentes e anteriores. Portanto, o estado anterior da entrada não tem nenhum efeito sobre o estado atual do circuito. Enquanto o circuito sequencial tem memória, a saída pode variar com base na entrada. Este tipo de circuito usa entrada, saída anterior, relógio e um elemento de memória. Aqui, os elementos de memória podem ser latch ou flip-flops. Os circuitos sequenciais são projetados por vários métodos, como usando ROMs e flips, PLAs, CPLDs (dispositivo lógico programável complexo) , FPGAs (Field Programmable Gate Array) . Neste artigo, vamos discutir apenas como projetar um circuito sequencial usando PLAs.

O diagrama de blocos do circuito sequencial conforme mostrado abaixo:

Diagrama de blocos do circuito sequencial

Projeto de circuito sequencial usando PLAs

Circuitos sequenciais pode ser realizado usando PLAs (Programmable Logic Arrays) e flip-flops. Nesse projeto, a atribuição de estado pode ser importante porque o uso de uma atribuição de bom estado pode reduzir o número necessário de termos do produto e, portanto, reduzir o tamanho necessário do PLA. Um termo de produto definido como a conjunção de literais, em que cada literal é uma variável ou sua negação.

Vamos considerar o projeto de um conversor de código. A tabela de estados mostrada abaixo na tabela pode ser realizada usando um PLA e três sandálias de dedo conforme mostrado na figura abaixo. Esta configuração de circuito é muito semelhante ao design baseado em flip-flop ROM, exceto que o ROM é substituído pelo PLA de tamanho adequado. A atribuição de estado leva à tabela verdade fornecida abaixo. Esta tabela poderia ser armazenada em um PLA com quatro entradas, 13 termos de produto e quatro saídas, mas isso ofereceria uma pequena redução no tamanho em comparação com a ROM de 16 palavras.

| X Q1 Q2 Q3 | Com D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 X X X X X X X X |

Tabela: Tabela da verdade

PRESENTE ESTADO

| PRÓXIMO ESTADO X = 0 1 | PRESENTE SAÍDA (Z) |

| PARA | B C | 1 0 |

B C | D E E E | 1 0 0 1 |

D É | H H H M | 0 1 1 0 |

H M | A A PARA - | 0 1 1 - |

Tabela: Tabela de estado

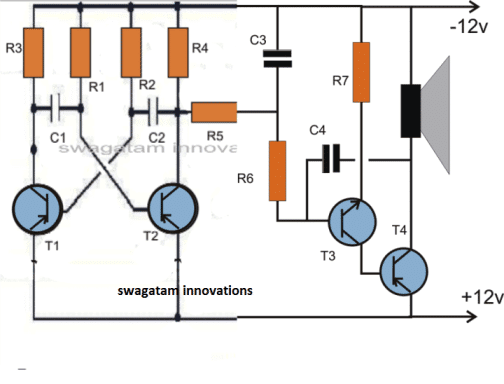

Projeto de circuitos sequenciais usando PLA

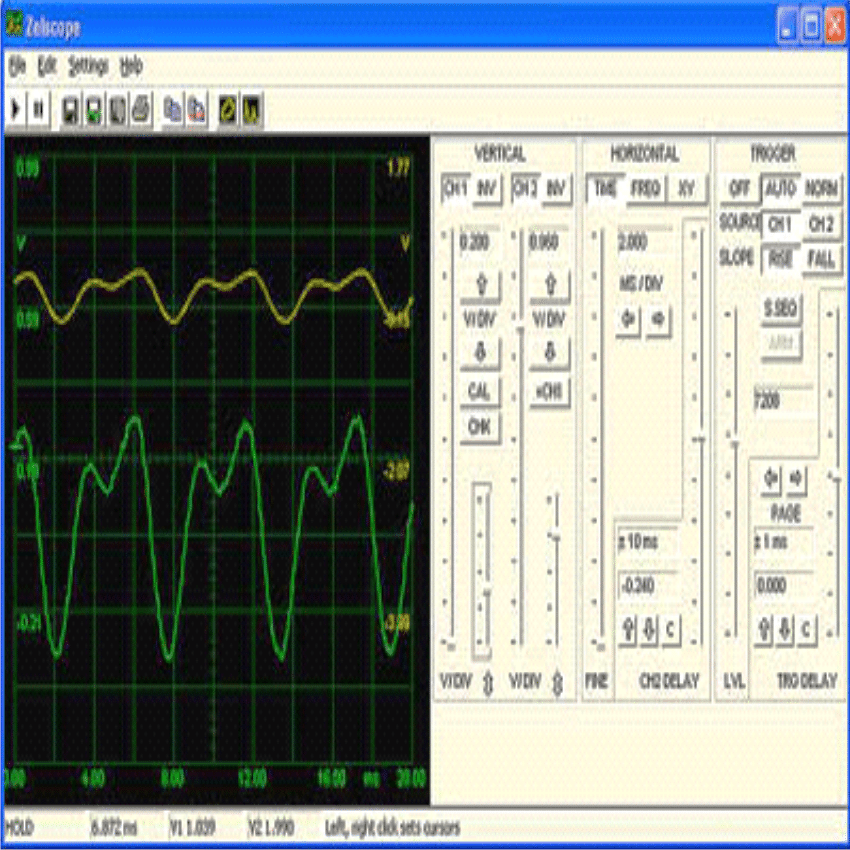

Equações de entrada e saída derivadas do mapa de Karnaugh

Aqui, como há sete estados, três flip-flops D são necessários. Portanto, é necessário um circuito PLA com 4 entradas e 4 saídas. Se a atribuição de estado do conversor de código for considerada, a equação de saída resultante e as equações de entrada de flip-flop D derivadas do Karnaugh podem ser escritas nas seguintes equações

D1 = Q1 + = Q2 ”

D2 = Q2 + = Q2 ”

D3 = Q3 + = Q1 Q2 Q3 = X ”Q1 Q3” = X Q1 ”Q2”

Z = X ”Q3” + X Q3

| X Q1 Q2 Q3 | Com D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 1 0 0 - 0 - - 0 onze

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

A tabela PLA que corresponde a essas equações é fornecida na tabela acima. Esta tabela pode ser realizada usando PLA com quatro entradas, sete termos de produto e quatro saídas. Para verificar a operação do projeto acima inicialmente, assuma que X = 0 e Q1Q2Q3 = 000. Isso seleciona as linhas - - 0- e 0 - - -0 na tabela, então Z = 0 e D1D2D3 = 100. Após a transição do clock ativo, Q1Q2Q3 = 100. Se a próxima entrada for X = 1, então as linhas - - 0 - e - 1- - serão selecionadas, então Z = 0 e D1D2D3 = 110. Após a transição do clock ativo, Q1Q2Q3 = 110.

Matriz Lógica Programável (PLA)

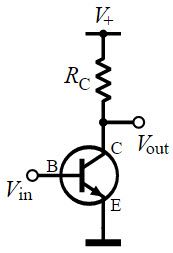

O array lógico programável é um dispositivo lógico programável. Geralmente é usado para implementar circuitos lógicos combinacionais. O PLA tem um conjunto de planos AND programáveis (array AND), que se conectam a um conjunto de planos OR programáveis (array OR), que podem então ser complementados provisoriamente para produzir uma saída. Este layout permite que um grande número de funções lógicas sejam sintetizadas no soma de produtos (SOP) formulários canônicos. Um diagrama de blocos simples de um PLA é fornecido abaixo.

Diagrama de blocos de um PLA

A principal diferença entre PLA e PAL (lógica de matriz programável) é,

PLA: Ambos Plano AND e plano OR são programáveis.

PAL: Apenas o plano AND é programável, enquanto o plano OR é fixo.

Para uma melhor compreensão do PLA, aqui estamos considerando o exemplo abaixo.

Vamos tentar implementar essas funções f1 e f2 são fornecidas como

As entradas x1, x2, x3 e seus respectivos sinais complementados são dados ao plano AND programável, lá obteremos as saídas do plano AND como mintermos P1, P2, P3 chamados. Então, esses sinais são dados ao plano OR programável para produzir as funções de saída necessárias f1 e f2 (soma dos produtos). A figura abaixo descreve a implementação de nível de porta do PLA para determinada funcionalidade.

Implementação do PLA

Trata-se de projeto de circuitos sequenciais usando PLA. Consideramos que as informações prestadas neste artigo são úteis para uma melhor compreensão deste conceito. Além disso, qualquer dúvida sobre este artigo ou qualquer ajuda em implementação de projetos elétricos e eletrônicos , você pode nos abordar comentando na seção de comentários abaixo. Aqui está uma pergunta para você, O que significa um circuito sequencial?