Um estágio de buffer basicamente um estágio intermediário reforçado que permite que a corrente de entrada alcance a saída sem ser afetada pelo carregamento de saída.

Nesta postagem, tentaremos entender o que são os buffers digitais, e daremos uma olhada em sua definição, símbolo, tabela verdade, inversão dupla usando porta lógica “NOT”, ventilador de saída de buffer digital, buffer tri-state, tri-state buffer switch equivalente, buffer tri-state ativo 'HIGH', buffer tri-state inversor ativo 'HIGH', buffer tri-state ativo 'LOW', buffer tri-state inversor ativo 'LOW', controle do buffer tri-state , controle de barramento de dados de buffer tri-state e, finalmente, daremos uma visão geral sobre o buffer digital comumente disponível e ICs de buffer tri-state.

Em um dos posts anteriores aprendemos sobre a porta lógica “NOT” que também é chamada de inversor digital. Em uma porta NOT, a saída é sempre complementar à entrada.

Portanto, se a entrada for “HIGH” a saída ficará “LOW”, se a entrada for “LOW” a saída ficará “HIGH”, então isso é chamado de inversor.

Pode haver uma situação em que a saída precisa ser separada ou isolada da entrada, ou nos casos em que a entrada pode ser bastante fraca e precisa acionar cargas que exigem corrente mais alta sem inverter a polaridade do sinal usando um relé ou transistor etc. Em tais situações, os buffers digitais tornam-se úteis e são efetivamente aplicados como buffers entre a fonte do sinal e o estágio real do driver de carga.

Tal portas lógicas que pode fornecer saída de sinal igual à entrada e atuar como estágio de buffer intermediário é chamado de buffer digital.

Um buffer digital não realiza nenhuma inversão do sinal alimentado e também não é um dispositivo de 'tomada de decisão', como a porta lógica “NÃO”, mas fornece a mesma saída como entrada.

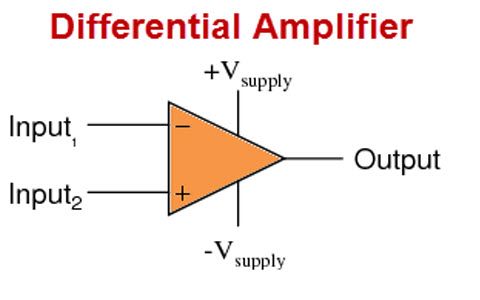

Ilustração do buffer digital:

O símbolo acima é semelhante à porta lógica “NOT” sem o “o” na ponta do triângulo, o que significa que não realiza nenhuma inversão.

A equação booleana para o buffer digital é Y = A.

“Y” é a entrada e a saída “A”.

Tabela da verdade:

Inversão dupla usando portas lógicas “NÃO”:

Um buffer digital pode ser construído usando duas portas lógicas 'NÃO' da seguinte maneira:

O sinal de entrada é primeiro invertido pela primeira porta NOT no lado esquerdo e o sinal invertido é então ainda mais invertido pela próxima porta 'NÃO' no lado direito, o que torna a saída igual à entrada.

Por que buffers digitais são usados

Agora você pode estar coçando sua cabeça porque o buffer digital ainda existe, ele não faz nenhuma operação como outras portas lógicas, nós poderíamos apenas jogar o buffer digital de um circuito e conectar um pedaço de fio… correto? Bem, na verdade não.

Aqui está a resposta : Uma porta lógica não requer alta corrente para realizar nenhuma operação. Requer apenas um nível de tensão (5V ou 0V) em baixa corrente é suficiente.

Todos os tipos de portas lógicas suportam principalmente um amplificador embutido, de forma que a saída não depende dos sinais de entrada. Se colocarmos duas portas lógicas 'NÃO' em cascata em série, obteremos a mesma polaridade de sinal da entrada no pino de saída, mas com uma corrente relativamente mais alta. Em outras palavras, o buffer digital funciona como um amplificador digital.

Um buffer digital pode ser usado como um estágio de isolamento entre os estágios do gerador de sinal e os estágios do driver e também ajuda a evitar que a impedância afete um circuito do outro.

Um buffer digital pode fornecer capacidade de corrente mais alta, que pode ser usada para conduzir transistores de chaveamento com mais eficiência.

O buffer digital oferece maior amplificação, também chamada de capacidade de “fan-out”.

Capacidade de fan-out do buffer digital:

ESPALHAM : O fan-out pode ser definido como o número de portas lógicas ou CIs digitais que podem ser acionados em paralelo por um buffer digital (ou quaisquer CIs digitais).

Um buffer digital típico possui fan-out de 10, o que significa que o buffer digital pode acionar 10 CIs digitais em paralelo.

FAN-IN : O fan-in é o número de entradas digitais que podem ser aceitas pela porta lógica digital ou IC digital.

No esquema acima, o buffer digital possui fan-in de 1, o que significa uma entrada. Uma porta lógica 'E' de ‘2 entradas’ possui fan-in de duas e assim por diante.

No esquema acima, um buffer é conectado às 3 entradas de três portas lógicas diferentes.

Se apenas conectarmos um pedaço de fio no lugar do buffer no circuito acima, o sinal de entrada pode não estar com corrente suficiente e faz com que a tensão caia nas portas e pode nem mesmo reconhecer o sinal.

Portanto, em conclusão, um buffer digital é usado para amplificar um sinal digital com saída de corrente mais alta.

Buffer Tri-state

Agora sabemos o que um buffer digital faz e por que existe em circuitos eletrônicos. Esses buffers têm dois estados “HIGH” e “LOW”. Existe outro tipo de buffer denominado “buffer tri-state”.

Este buffer tem um pino adicional denominado “pino de ativação”. Usando o pino de habilitação, podemos conectar ou desconectar a saída da entrada eletronicamente.

Como um buffer normal, ele funciona como amplificador digital e fornece sinal de saída igual ao sinal de entrada, a única diferença é que a saída pode ser conectada e desconectada eletronicamente pelo pino de habilitação.

Portanto, um terceiro estado é introduzido, neste a saída não é nem “HIGH” nem “LOW”, mas um estado de circuito aberto ou alta impedância na saída e não responderá aos sinais de entrada. Este estado é conhecido como “HIGH-Z” ou “HI-Z”.

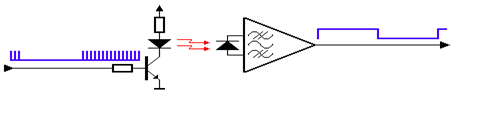

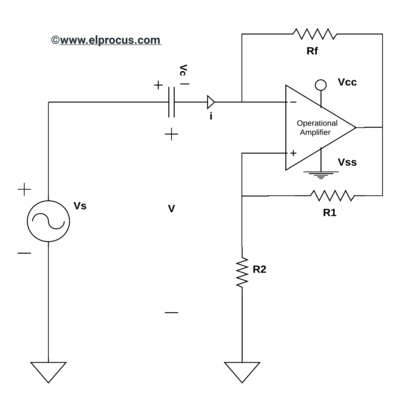

O acima é o circuito equivalente do buffer tri-state. O pino de habilitação pode conectar ou desconectar a saída da entrada.

Existem quatro tipos de buffer Tri-state:

• Buffer tri-state 'HIGH' ativo

• Buffer tri-state “LOW” ativo

• Buffer tri-state de inversão 'HIGH' ativo

• Buffer tri-state de inversão 'BAIXO' ativo

Vamos examinar cada um deles sequencialmente.

Buffer tri-state 'HIGH' ativo

No buffer tri-state ativo “HIGH” (por exemplo: 74LS241) o pino de saída é conectado ao pino de entrada quando aplicamos “HIGH” ou “1” ou sinal positivo no pino de habilitação.

Se aplicarmos “LOW” ou “0” ou sinal negativo ao pino de habilitação, a saída será desconectada da entrada e vai para o estado “HI-Z”, onde a saída não responderá à entrada e a saída estará em estado de circuito aberto.

Buffer tri-state 'LOW' ativo

Aqui, a saída será conectada à entrada quando aplicamos “LOW” ou “0” ou sinal negativo no pino de habilitação.

Se aplicarmos “HIGH” ou “1” ou sinal positivo para habilitar o pino, a saída será desconectada da entrada e a saída estará no estado “HI-Z” / estado de circuito aberto.

Mesa da verdade:

Buffer tri-state de inversão 'HIGH' ativo

No buffer Tri-state de inversão “HIGH” ativo (exemplo: 74LS240), a porta age como uma porta lógica “NÃO”, mas com o pino de habilitação.

Se aplicarmos “HIGH” ou “1” ou sinal positivo na entrada de habilitação, a porta é ativada e age como uma porta lógica “NÃO” normal, onde sua saída é inversão / complementar da entrada.

Se aplicarmos “LOW” ou “0” ou sinal negativo ao pino de habilitação, a saída estará em “HI-Z” ou estado de circuito aberto.

Tabela da verdade:

Buffer tri-state de inversão 'LOW' ativo:

No buffer Tri-state de inversão “LOW” ativo, a porta atua como uma porta lógica “NÃO”, mas com o pino de habilitação.

Se aplicarmos “LOW” ou “0” ou sinal negativo para habilitar o pino, o gate será ativado e funcionará como o gate lógico regular “NOT”.

Se aplicarmos “HIGH” ou “1” ou sinal positivo para habilitar o pino, o pino de saída estará no estado “HI-Z” / estado de circuito aberto.

Mesa da verdade:

Controle de buffer tri-state:

Do acima, vimos que um buffer pode fornecer amplificação digital e buffers de três estados podem desconectar completamente sua saída da entrada e fornecer um estado de circuito aberto.

Nesta seção, aprenderemos sobre a aplicação do buffer tri-state e como ele é usado em circuitos digitais para gerenciar a comunicação de dados de forma eficiente.

Em circuitos digitais, podemos encontrar um barramento de dados / fios transportando dados, eles transportam todos os tipos de dados em um único barramento para reduzir o congestionamento da fiação / reduzir traços de PCB e também reduzir o custo de fabricação.

Em cada extremidade do barramento, vários dispositivos lógicos, microprocessadores e microcontroladores estão conectados, os quais tentam se comunicar simultaneamente, o que cria algo chamado contenção.

A contenção ocorre em um circuito quando alguns dispositivos em um barramento acionam “HIGH” e alguns dispositivos acionam “LOW” simultaneamente, o que causa curto-circuito e causa danos em um circuito.

O buffer tri-state pode evitar tal contenção e enviar e receber dados de maneira adequada por meio de um barramento.

O buffer tri-state é usado para isolar dispositivos lógicos, microprocessadores e microcontroladores uns dos outros em um barramento de dados. Um decodificador permitirá que apenas um conjunto de buffers de três estados passe dados pelo barramento.

Digamos que o conjunto de dados “A” esteja conectado a um microcontrolador, o conjunto de dados “B” a um microprocessador e o conjunto de dados “C” a alguns circuitos lógicos.

No esquema acima, todos os buffers são buffer tri-state alto ativo.

Quando o decodificador define o ENA “HIGH” o conjunto de dados “A” é habilitado, agora o microcontrolador pode enviar dados através do barramento.

O restante dos dois conjuntos de dados “B” e “C” estão em “HI-Z” ou estado de impedância muito alta que isola eletricamente o microprocessador e os circuitos lógicos do barramento, que atualmente é usado pelo microcontrolador.

Quando o decodificador define ENB como 'HIGH', o conjunto de dados 'B' pode enviar dados pelo barramento e o restante dos conjuntos de dados 'A' e 'C' são isolados do barramento no estado 'HI-Z'. Da mesma forma, para quando o conjunto de dados “C” estiver habilitado.

O barramento de dados é usado por qualquer um dos conjuntos de dados “A” ou “B” ou “C” em um determinado momento para evitar contenção.

Também podemos estabelecer comunicação duplex (bidirecional) conectando dois buffers tri-state em paralelo e na direção oposta. Os pinos de habilitação podem ser usados como controle de direção. Para esse tipo de aplicações, o IC 74245 pode ser utilizado.

Aqui está a lista comumente disponível de buffers digitais e buffers Tri-state:

• 74LS07 Tampão Hex não inversor

• 74LS17 Hex Buffer / Driver

• 74LS244 Octal Buffer / Line Driver

• 74LS245 Octal Bidirecional Buffer

• Tampão CD4050 Hex não inversor

• CD4503 Hex Tri-state Buffer

• HEF40244 Tri-state Octal Buffer

Isso conclui nossa discussão sobre como funcionam os buffers digitais e suas várias configurações digitais. Espero que tenha ajudado você a entender bem os detalhes. Se você tiver mais perguntas ou sugestões, expresse suas dúvidas na seção de comentários. Você pode obter uma resposta rápida.

Anterior: Como funcionam os portões lógicos Próximo: Noções básicas sobre resistores pull-up e pull-down com diagramas e fórmulas