Para a execução de um programa de computador, é necessário o funcionamento síncrono de mais de um componente de um computador. Por exemplo, Processadores - fornecer informações de controle necessárias, endereços ... etc, barramentos - para transferir informações e dados de e para a memória para dispositivos de E / S ... etc. O fator interessante do sistema seria a maneira como ele lida com a transferência de informações entre processador, memória e dispositivos de E / S. Normalmente, os processadores controlam todo o processo de transferência de dados, desde o início da transferência até o armazenamento dos dados no destino. Isso adiciona carga ao processador e na maioria das vezes ele permanece no estado ideal, diminuindo a eficiência do sistema. Para acelerar a transferência de dados entre os dispositivos de E / S e a memória, o controlador DMA atua como mestre da estação. O controlador DMA transfere dados com intervenção mínima do processador.

O que é um controlador DMA?

O termo DMA significa acesso direto à memória. O dispositivo de hardware usado para acesso direto à memória é chamado de controlador DMA. DMA controlador é uma unidade de controle , parte do dispositivo de I / O circuito de interface , que pode transferir blocos de dados entre dispositivos de E / S e a memória principal com intervenção mínima do processador.

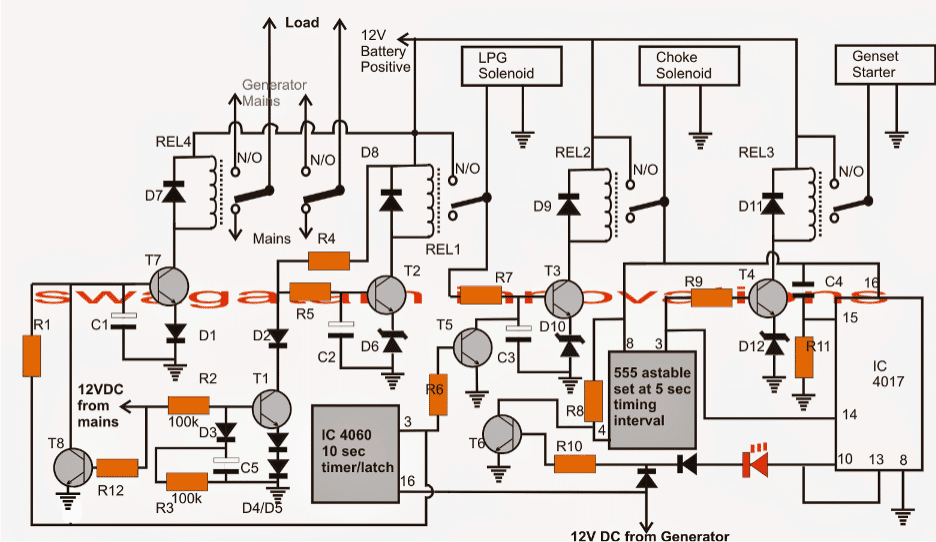

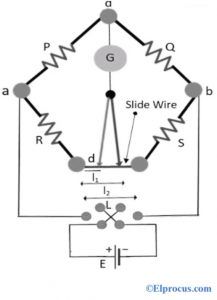

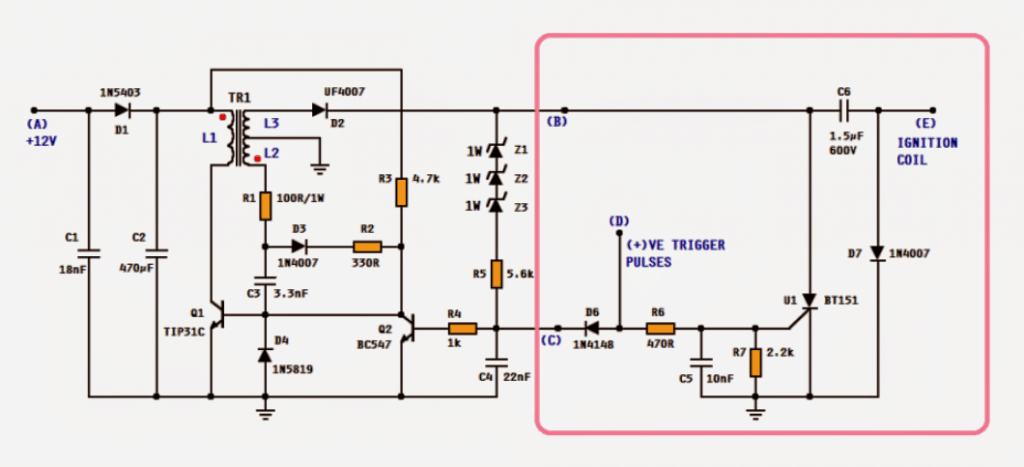

Diagrama do controlador DMA em arquitetura de computador

O controlador DMA fornece uma interface entre o barramento e os dispositivos de entrada-saída. Embora transfira dados sem intervenção do processador, ele é controlado pelo processador. O processador inicia o controlador DMA enviando o endereço inicial, o número de palavras no bloco de dados e a direção da transferência de dados. de dispositivos de E / S para a memória ou da memória principal para dispositivos de E / S. Mais de um dispositivo externo pode ser conectado ao controlador DMA.

DMA em Arquitetura de Computadores

O controlador DMA contém uma unidade de endereço, para gerar endereços e selecionar o dispositivo de E / S para transferência. Ele também contém a unidade de controle e a contagem de dados para manter a contagem do número de blocos transferidos e indicar a direção da transferência dos dados. Quando a transferência é concluída, o DMA informa o processador levantando uma interrupção. O diagrama de blocos típico do controlador DMA é mostrado na figura abaixo.

Diagrama de blocos típico do controlador DMA

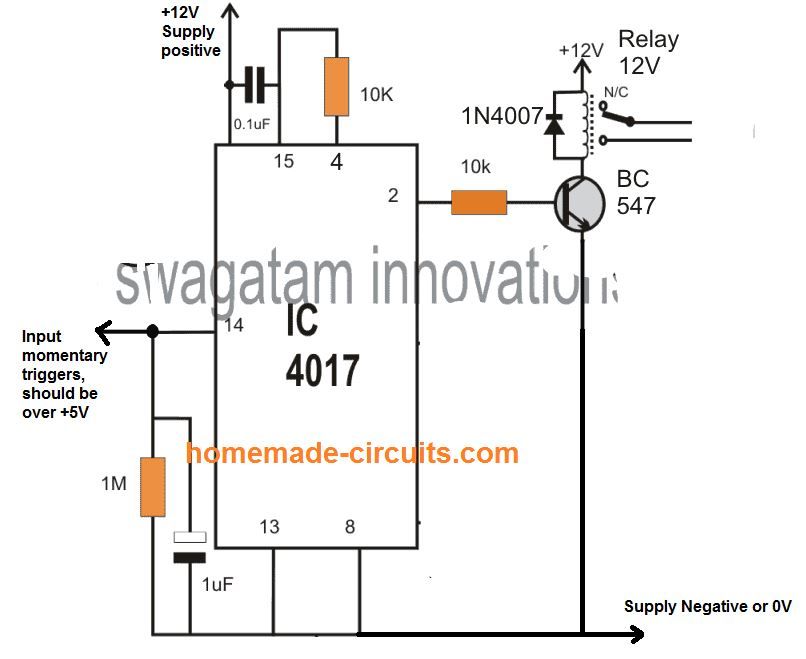

Trabalho do controlador DMA

O controlador DMA precisa compartilhar o barramento com o processador para fazer a transferência de dados. O dispositivo que mantém o barramento em um determinado momento é denominado barramento mestre. Quando uma transferência do dispositivo I / O para a memória ou vice-versa deve ser feita, o processador para a execução do programa atual, incrementos o programa contador, move os dados sobre a pilha e depois envia um sinal de seleção de DMA para o controlador de DMA pelo barramento de endereço.

Se o controlador DMA estiver livre, ele solicita o controle do barramento do processador, aumentando o sinal de solicitação do barramento. O processador concede o barramento ao controlador aumentando o sinal de concessão do barramento, agora o controlador DMA é o barramento mestre. O processador inicia o controlador DMA enviando os endereços de memória, o número de blocos de dados a serem transferidos e a direção da transferência de dados. Depois de atribuir a tarefa de transferência de dados ao controlador DMA, em vez de esperar idealmente até a conclusão da transferência de dados, o processador retoma a execução do programa após recuperar as instruções da pilha.

Transferência de dados no computador por controlador DMA

O controlador DMA agora tem o controle total dos barramentos e pode interagir diretamente com a memória e os dispositivos de E / S independentes da CPU. Faz a transferência de dados de acordo com as instruções de controle recebidas pelo processador. Após a conclusão da transferência de dados, ele desativa o sinal de solicitação de barramento e a CPU desativa o sinal de concessão de barramento, movendo o controle dos barramentos para a CPU.

Quando um dispositivo de E / S deseja iniciar a transferência, ele envia um sinal de solicitação DMA ao controlador DMA, para o qual o controlador confirma se está livre. Em seguida, o controlador solicita ao processador o barramento, aumentando o sinal de solicitação do barramento. Depois de receber o sinal de concessão de barramento, ele transfere os dados do dispositivo. Para n controlador DMA canalizado, um número n de dispositivos externos pode ser conectado.

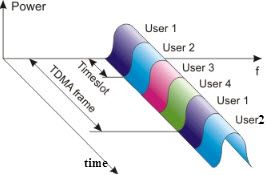

O DMA transfere os dados em três modos, que incluem o seguinte.

para) Modo Burst : Neste modo, o DMA transfere os barramentos para a CPU somente após a conclusão da transferência de todos os dados. Enquanto isso, se a CPU precisar do barramento, ela deve permanecer ideal e aguardar a transferência de dados.

b) Modo Cycle Stealing : Neste modo, o DMA dá o controle dos barramentos à CPU após a transferência de cada byte. Ele emite continuamente uma solicitação de controle de barramento, faz a transferência de um byte e retorna o barramento. Por esta CPU não tem que esperar muito tempo se precisar de um bus para tarefa de maior prioridade.

c) Modo Transparente: Aqui, o DMA transfere dados apenas quando a CPU está executando a instrução que não requer o uso de barramentos.

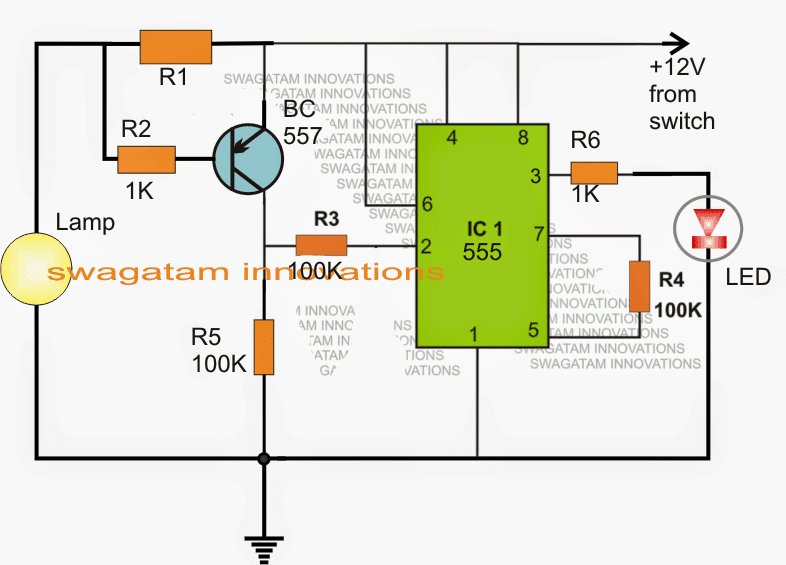

8237 Controlador DMA

- 8237 tem 4 canais de E / S junto com a flexibilidade de aumentar o número de canais.

- Cada canal pode ser programado individualmente e tem um endereço de 64k e capacidade de dados.

- O bloco de controle de tempo, bloco de controle de comando de programa e bloco codificador de prioridade são os três blocos principais de 8237A.

- Os sinais de controle de tempo interno e externo são acionados pelo bloco de controle de tempo.

- Vários comandos dados pelo microprocessador ao DMA são decodificados pelo bloco de controle de comando do programa.

- Qual canal deve receber a prioridade mais alta é decidido pela prioridade bloco codificador .

8237A tem 27 registros internos.

8237A opera em dois ciclos- ciclo ideal e ciclo ativo, onde cada ciclo contém 7 estados separados compostos por um período de clock cada.

S0- O primeiro estado, onde o controlador solicitou o barramento e está aguardando o reconhecimento do processador.

S1, S2, S3, S4 são chamados de estados de trabalho do 8237A, onde ocorre a transferência real de dados. Se for necessário mais tempo para os estados de espera de transferência, SW será adicionado entre esses estados.

Para transferência de memória para memória, as transferências de leitura da memória e gravação para memória devem ser feitas. Oito estados são necessários para uma transferência única. Os primeiros quatro estados com subscritos S11, S12, S13, S14 fazem a transferência de leitura da memória e os próximos quatro S21, S22, S23, S24 são para transferência de escrita para a memória.

O DMA entra no estado ideal quando nenhum canal está solicitando serviço e executa o estado do SI. SI é um estado inativo em que o DMA está inativo até receber uma solicitação. Nesse estado, o DMA está na condição de programa, em que o processador pode programar o DMA.

Quando o DMA está no estado ideal e não recebe mais solicitações de canal, ele envia um sinal HRQ para o processador e entra no estado Ativo, onde pode iniciar a transferência de dados pelo modo burst, modo de roubo de ciclo ou modo transparente.

8237 Pin Diagrama

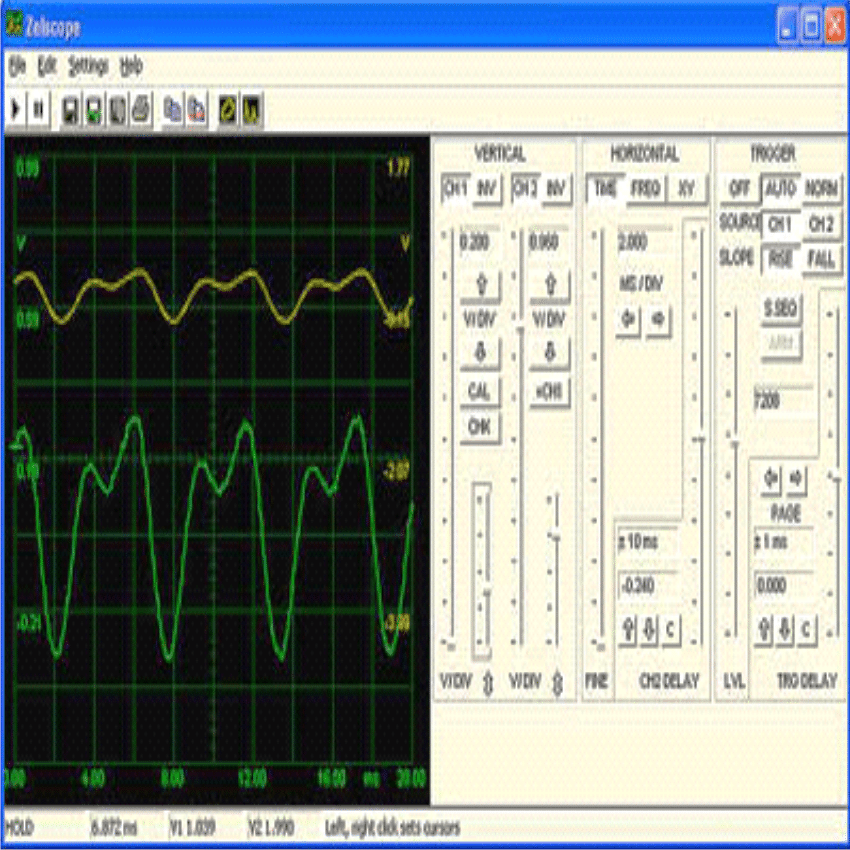

8257 Controlador DMA

Quando emparelhado com um único dispositivo de porta I / O Intel 8212, o controlador 8257 DMA forma um canal completo de 4 Controlador DMA . Ao receber uma solicitação de transferência, o controlador 8257-

- Adquire o controle sobre o barramento do sistema do processador.

- O periférico conectado ao canal de prioridade mais alta é reconhecido.

- Os bits menos significativos do endereço de memória são movidos pelas linhas de endereço A0-A7 do barramento do sistema.

- O mais significativo 8 bits do endereço de memória são direcionados para a porta de E / S 8212 por meio de linhas de dados.

- Gera os sinais de controle apropriados para a transferência de dados entre periféricos e locais de memória endereçados.

- Quando o número especificado de bytes é transferido, o controlador informa o término da transferência da CPU ativando a saída de contagem de terminal (TC).

Para cada canal, 8257 contém dois Registros de 16 bits - 1) Registro de endereço DMA e 2) Registro de contagem de terminal, que deve ser inicializado antes que um canal seja habilitado. O endereço do primeiro local de memória a ser acessado é carregado no registro de endereço DMA. Os 14 bits de ordem inferior do valor carregado no registro de contagem de terminal indicam o número de ciclos de DMA menos um antes da ativação da saída de contagem de terminal. O tipo de operação de um canal é indicado pelos dois bits mais significativos do registro de contagem do Terminal.

Diagrama de pinos 8257

Vantagens e desvantagens do controlador DMA

As vantagens e desvantagens do controlador DMA incluem o seguinte.

Vantagens

- O DMA acelera as operações de memória, evitando o envolvimento da CPU.

- A sobrecarga de trabalho na CPU diminui.

- Para cada transferência, apenas alguns poucos ciclos de clock são necessários

Desvantagens

- O problema de coerência do cache pode ser visto quando o DMA é usado para transferência de dados.

- Aumenta o preço do sistema.

DMA ( Acesso direto à memória ) O controlador está sendo usado em placas de vídeo, placas de rede, placas de som, etc. O DMA também é usado para transferência intra-chip em processadores multi-core. Operando em um de seus três modos, o DMA pode reduzir consideravelmente a carga do processador. Em qual dos modos de DMA você trabalhou? Qual modo você considera mais eficaz?