O ARM (Advanced RISC Machine) lançou vários processadores que possuem diferentes recursos, bem como os diferentes núcleos para uma ampla variedade de aplicações. O primeiro projeto de arquitetura ARM tem processadores de 26 bits, mas agora chegou aos processadores de 64 bits. A expansão geral dos produtos ARM não pode ser categorizada em algumas informações específicas. Mas os produtos ARM podem ser entendidos com base em sua arquitetura. Os processadores da série ARM padrão disponíveis no mercado vão do ARM7 ao ARM11. Esses processadores têm vários recursos como cache, memória Data Tightly Coupled, MPU, MMU, etc. Algumas das séries de processadores ARM mais conhecidas são ARM926EJ-S, ARM7TDMI e ARM11 MPCore. Este artigo se destina especialmente à visão geral da arquitetura do microcontrolador LPC2148 baseado em ARM7, que fornecerá informações breves sobre o microcontrolador arquitetura.

Arquitetura do microcontrolador LPC2148 baseada em ARM7

O ARM7 é um dispositivo de uso geral de 32 bits microprocessador , e oferece alguns dos recursos como pouca utilização de energia e alto desempenho. A arquitetura de um ARM depende do princípios de RISC . O mecanismo de decodificação associado, bem como o conjunto de instruções RISC- são muito fáceis quando comparamos com microprogrammed CISC - Computadores de conjunto de instruções complexas.

O método Pipeline é usado para processar todos os blocos da arquitetura. Em geral, um único conjunto de instruções está sendo executado, então seu descendente está sendo traduzido e um 3rd- a instrução está sendo obtida da memória.

Um exclusivo plano arquitetônico de ARM7 é chamado de Thumb, e é perfeitamente adequado para aplicações de alto volume onde a compactação do código é uma questão. O ARM7 também usa uma arquitetura exclusiva chamada Thumb. Torna-o perfeitamente adequado para diferentes aplicações por limitações de memória onde a densidade do código é uma questão.

Arquitetura do microcontrolador baseado em ARM7 (LPC2148)

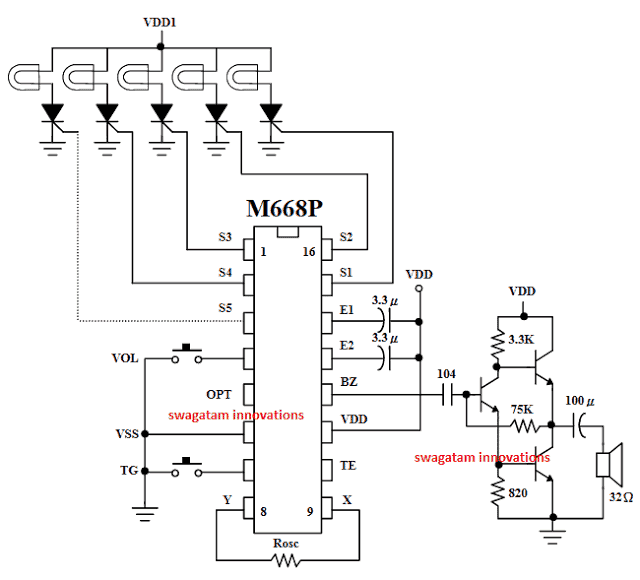

Fontes de interrupção

Cada dispositivo periférico consiste em uma única linha de interrupção aliada ao VIC (controlador de interrupção de vetor), embora possa ter vários sinalizadores de interrupção dentro. Sinalizadores de interrupção individuais também podem significar um ou mais recursos de interrupção.

Memória de programa flash on-chip

O microcontrolador LPC2141 / 42/44/46/48 inclui uma memória flash como 32 kilobytes, kilobytes, 128 kilobytes, 256 kilobytes respectivamente. Esta memória flash pode ser usada tanto para armazenamento de dados quanto para código. A programação da memória flash pode ser feita no sistema através da porta serial.

O aplicativo do programa também pode apagar enquanto o aplicativo do programa está em execução, permitindo flexibilidade de melhorias de firmware do campo de armazenamento de dados, etc. Por causa da seleção de uma solução arquitetônica para um bootloader on-chip, a memória disponível para os microcontroladores LPC2141 / 42 / 44/46/48 é de 32 kilobytes, kilobytes, 128 kilobytes, 256 kilobytes e 500 kilobytes. A memória flash desses microcontroladores oferece 1.00.000 apagamento por ciclos e preservação de dados por muitos anos.

Bloco de conexão por pino

Este bloco permite a escolha de pinos do microcontrolador LPC2148 baseado em ARM7 por ter várias funções. Os multiplexadores pode ser controlado pelos registradores de configuração para permitir o link entre o pino e também os periféricos no chip.

Os periféricos devem ser acoplados aos pinos adequados antes de serem disparados e antes de qualquer interrupção conectada ser permitida. A funcionalidade do microcontrolador pode ser definida pelo módulo de controle de pinos por sua seleção de registros de pinos em um determinado ambiente de hardware.

Depois de reorganizar, todos os pinos das portas (porta 0 e porta 1) são organizados como i / p pelas exceções fornecidas. Se a depuração for permitida

Se a depuração for permitida, os pinos do JTAG adivinharão a funcionalidade do JTAG. Se um rastreamento for permitido, os pinos de rastreamento adivinharão a funcionalidade do rastreamento. Os pinos conectados aos pinos I2C0 e I2C1 são dreno aberto.

GPIO- Entrada / saída paralela de uso geral

Os registros GPIO controlam os pinos do dispositivo que não estão vinculados a uma função periférica específica. Os pinos do dispositivo podem ser organizados como i / p [s ou o / ps. Os registros individuais permitem limpar qualquer número de o / p simultaneamente. O valor do registro de saída pode ser lido de volta e a condição atual dos pinos da porta. Esses microcontroladores iniciam uma função acelerada nos dispositivos LPC200.

Os registros de entrada / saída de uso geral são movidos para o barramento do processador usado para o melhor tempo de E / S provável.

- Esses registros são bytes endereçáveis.

- O valor total de uma porta pode ser

- O valor completo da porta pode ser escrito na única instrução

ADC de 10 bits (conversor analógico para digital)

Os microcontroladores como LPC2141 ou 42 incluem dois Conversores ADC , e estes são apenas de 10 bits com um e o LPC2144 / 46/48 tem dois ADCs, e estes são apenas ADCs de aproximação direta de 10 bits. Embora ADC0 inclua 6 canais e ADC1 tenha 8 canais. Assim, o número de ADC i / ps acessíveis para LPC2141 ou 42 é 6 e 14 para LPC2141 ou 42.

DAC de 10 bits (conversor digital para analógico)

O DAC permite que esses microcontroladores produzam um o / p e V analógico mutávelREFé a melhor saída de um digital para analógico Tensão.

Device Controller-USB 2.0

O barramento serial universal consiste em 4 fios e fornece suporte para comunicação entre diversos periféricos e hosts. Este controlador permite a largura de banda de USB para conectar dispositivos usando um protocolo baseado no token.

O barramento suporta a desconexão de conexão a quente e coleta dinâmica dos dispositivos. Cada comunicação é iniciada por meio do controlador de host. Esses microcontroladores são projetados com um controlador de aparelho de barramento serial universal que permite a substituição de dados de 12 Mbit / s por um controlador host de USB.

UARTs

Esses microcontroladores incluem dois UARTs para linhas de transmissão e obtenção de dados padrão. Em comparação com microcontroladores anteriores (LPC2000), UARTs em microcontroladores LPC2141 / LPC2142 / LPC2144 / LPC2146 / LPC2148 iniciam um gerador de taxa de transmissão parcial usado para ambos os UARTs, permitindo que esses tipos de microcontroladores alcancem taxas de transmissão típicas como 115200 por cada frequência de cristal acima de 2 MHz . Além disso, as funções de controle como CTS / RTS são totalmente executadas em hardware.

Controlador de E / S serial do barramento I2C

Cada microcontrolador de LPC2141 / LPC2142 / LPC2144 / LPC2146 / LPC2148 inclui dois I2C controladores de barramento, e isso é bidirecional. O controle inter-IC pode ser feito com a ajuda de dois fios, ou seja, um SCL e um SDA. Aqui, o SDA e SCL são a linha de relógio serial e a linha de dados serial

Cada aparelho é identificado por um endereço individual. Aqui, transmissores e receptores podem funcionar em dois modos, como modo mestre / modo escravo. Este é um bus multi-master e pode ser gerido por um ou mais bus masters ligados a ele. Esses microcontroladores suportam taxas de bits de até 400 kbit / s.

Controlador de entrada / saída serial SPI

Esses microcontroladores incluem um único controlador SPI e destinam-se a lidar com vários mestres e escravos associados a um barramento específico.

Simplesmente um mestre e um escravo podem conversar pela interface durante a transmissão de dados especificada. Durante isso, o mestre constantemente transmite um byte de dados para o escravo, assim como o escravo constantemente transmite dados para o mestre.

Controlador de entrada / saída serial SSP

Esses microcontroladores contêm SSP único e esse controlador é capaz de processar em um SPI, barramento de Microfio ou SSI de 4 fios. Ele pode se comunicar com o ônibus de vários mestres, bem como escravos

Mas, simplesmente um mestre particular, bem como escravo, pode conversar no barramento durante uma transmissão de dados especificada. Este microcontrolador suporta transferências full-duplex, por quadros de dados de 4-16 bits usados para o fluxo de dados do mestre - o escravo, bem como do escravo - o mestre.

Temporizadores / contadores

Cronômetros e contadores são projetados para contar os ciclos de PCLK (clock periférico) e, opcionalmente, produzir interrupções com base em registros de 4 partidas.

E compreende quatro i / ps de captura para capturar o valor de um temporizador quando um sinal i / p muda. Vários pinos podem ser escolhidos para executar uma captura específica. Esses microcontroladores podem calcular eventos externos nas entradas de captura se o menor pulso externo for equivalente. Nesse arranjo, as linhas de captura ociosas podem ser escolhidas como a captura de temporizador usual i / ps.

Watchdog Timer

O cronômetro de watchdog é usado para reiniciar o microcontrolador em um período de tempo razoável. Quando for permitido, o cronômetro produzirá uma reinicialização de um sistema se o programa do consumidor não conseguir recarregar o cronômetro em um período fixo de tempo.

RTC-Relógio em tempo real

O RTC tem como objetivo fornecer contadores para calcular o tempo quando o método de operação normal ou ocioso é escolhido. O RTC usa uma pequena quantidade de energia e é projetado para arranjos de bateria apropriados, onde a unidade de processamento central não está funcionando constantemente

Controle de poder

Esses microcontroladores suportam dois modos de energia condensada, como modo de desligamento e modo inativo. No modo Inativo, a execução das instruções é balanceada até que ocorra uma interrupção ou RST. As funções do periférico mantêm a operação durante o modo inativo e podem produzir interrupções para fazer com que a CPU reinicie o acabamento. O modo inativo remove a energia utilizada pela CPU, controladores, sistemas de memória e barramentos internos.

No modo de desligamento, o oscilador é desativado e o IC não recebe relógios internos. Os registradores periféricos, condição do processador com registradores, valores internos de SRAM são conservados durante o modo de desligamento e os pinos de saída dos níveis lógicos do chip permanecem fixos.

Este modo pode ser terminado e o processo comum reiniciado por interrupções específicas que são capazes de funcionar sem relógios. Como a operação do chip é balanceada, o modo Power-down diminui a utilização de energia do chip para quase zero.

PWM -Pulse Width Modulator

Os PWMs são baseados no bloco de cronômetro normal e também vêm em todos os recursos, embora simplesmente a função de modulador de largura de pulso seja fixada nos microcontroladores como LPC2141 / 42/44/46/48.

O cronômetro se destina a calcular os ciclos de PCLK (clock periférico) e, opcionalmente, produzir interrupções quando determinados valores do cronômetro surgem com base em registros de 7 partidas, e a função PWM também depende dos eventos de registro de correspondência.

A capacidade de controlar individualmente as posições de limite de aumento e diminuição permite que a modulação de largura de pulso seja utilizada para várias aplicações. Por exemplo, o controle de motor típico com multifásico usa 3 saídas não sobrepostas de PWM por controle separado de cada largura de pulso, bem como posições.

Barramento VPB

O divisor VPB resolve a associação entre o CCLK (clock do processador) e o PCLK (clock usado por dispositivos periféricos). Este divisor é usado para dois propósitos. O primeiro uso é fornecer periféricos pelo PCLK preferencial usando barramento VPB para que possam trabalhar na velocidade selecionada do processador ARM. Para conseguir isso, a velocidade deste barramento pode ser reduzida a taxa de clock do processador de 1⁄ 2 -1⁄ 4.

Porque este barramento deve funcionar com precisão na inicialização, e o estado padrão em RST (redefinir) é para o barramento trabalhar a 1⁄ 4o da taxa de clock do processador. O segundo uso disso é permitir economia de energia sempre que um aplicativo não precisar de nenhum periférico para funcionar na taxa de processador completa. Como o divisor VPB está associado à saída do PLL, ele permanece ativo durante o modo inativo.

Emulação e depuração

O microcontrolador (LPC2141 / 42/44/46/48) mantém emulação e depuração através da porta serial-JTAG. Uma porta de rastreamento permite rastrear a execução do programa. Funções de rastreamento e conceitos de depuração são multiplexados com port1 e GPIOs.

Segurança de código

O recurso de segurança de código desses microcontroladores LPC2141 / 42/44/46/48 permite uma função para controlar se ele pode ser protegido ou depurado durante a inspeção.

Portanto, tudo se resume à arquitetura do microcontrolador LPC2148 baseada em ARM7. Finalmente, do artigo acima, podemos concluir que ARM é uma arquitetura usada em vários processadores e também em microcontroladores. Aqui está uma pergunta para você, qual é a arquitetura de um processador ARM?