A ECL (lógica acoplada ao emissor) foi inventada pela primeira vez na IBM em agosto de 1956 por Hannon S. Yourke. Essa lógica também é conhecida como lógica de modo atual, usada nos computadores da IBM 7090 e 7094. A família ECL é muito rápida em comparação com lógica digital famílias. Geralmente, esta família lógica fornece um atraso de propagação inferior a 1 ns. É uma família lógica baseada em transistores de junção bipolar. É o circuito da família lógica mais rápido que é acessível para projetar um sistema lógico convencional. Este artigo apresenta uma visão geral de um circuito lógico acoplado ao emissor , trabalhando com aplicativos.

O que é Lógica Acoplada ao Emissor?

A lógica acoplada ao emissor é a melhor BJT família lógica baseada no projeto de sistema lógico convencional. Às vezes, também é chamado de lógica de modo atual, que é uma tecnologia digital de alta velocidade. Geralmente, o ECL é considerado o IC lógico mais rápido, onde atinge sua operação de alta velocidade usando uma oscilação de tensão muito pequena e também evitando que os transistores entrem na região de saturação.

Uma implementação de ECL utiliza uma tensão de alimentação positiva que é conhecida como PECL ou ECL de referência positiva. Nas primeiras portas ECL, uma alimentação de tensão negativa é usada devido à imunidade ao ruído. Depois disso, a ECL de referência positiva tornou-se muito famosa devido aos seus níveis lógicos mais compatíveis em comparação com as famílias lógicas TTL.

A lógica acoplada ao emissor dissipa uma enorme quantidade de energia estática, no entanto, seu consumo geral de corrente é baixo em comparação com CMOS em altas frequências. Assim, ECL é principalmente benéfico em circuitos de distribuição de clock e aplicações baseadas em alta frequência.

Recursos de Lógica Acoplada ao Emissor

Os recursos do ECL farão com que sejam usados em muitos aplicativos baseados em alto desempenho.

- A ECL fornece duas saídas que são sempre complementares uma da outra, pois o funcionamento do circuito é baseado em um amplificador diferencial.

- Esta família lógica é adequada principalmente para métodos de fabricação monolíticos porque os níveis lógicos são uma função das relações dos resistores.

- Os dispositivos da família ECL geram a saída correta e complementar da função proposta sem o uso de inversores externos. Consequentemente, diminui a contagem de pacotes e os requisitos de energia e também diminui os problemas que ocorrem por atrasos de tempo.

- Dispositivos ECL em design de amplificador diferencial oferecem ampla flexibilidade de desempenho, de modo que os circuitos ECL permitem ser usados tanto como circuitos digitais quanto lineares.

- O design da porta ECL tem normalmente alta e baixa impedância de entrada, o que é extremamente propício para alcançar grande fan-out, bem como capacidade de acionamento.

- Os dispositivos ECL geram um dreno de corrente constante na fonte de alimentação para simplificar o projeto da fonte de alimentação.

- Os dispositivos de ECL, incluindo saídas de emissor aberto, simplesmente permitem que incluam a capacidade de acionamento da linha de transmissão.

Circuito Lógico Acoplado ao Emissor

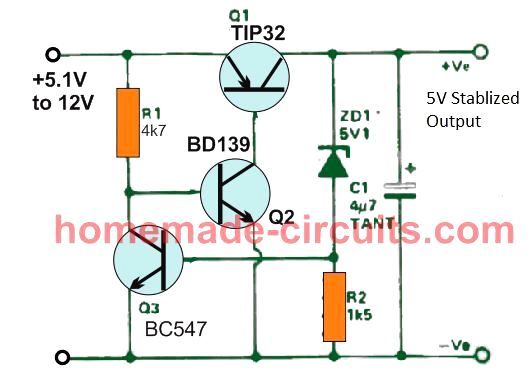

O circuito lógico acoplado ao emissor para o inversor é mostrado abaixo, que é projetado com resistores e transistores. Neste circuito, os terminais emissores de dois transistores são simplesmente conectados à resistência limitadora de corrente RE, que é usada para evitar que o transistor entre em saturação. Aqui a saída do transistor é retirada do terminal do coletor em vez do terminal do emissor. Este circuito fornece duas saídas Vout (saída inversora) e Vout2 (saída não inversora) e o terminal de entrada como Vin onde a entrada alta ou baixa é fornecida. +Vcc = 5V.

Como funciona a lógica acoplada ao emissor?

A operação da lógica acoplada ao emissor é que, sempre que a entrada HIGH for fornecida ao circuito ECL, ele fará com que o transistor 'Q1' LIGADO e o transistor Q2 DESLIGADO, mas o transistor Q1 não está saturado. Portanto, isso puxará a saída VOUT2 para HIGH e o valor da saída VOUT1 será LOW por causa da queda dentro de R1.

Da mesma forma, quando o valor VIN dado a ECL é BAIXO, então ele fará o transistor Q1 DESLIGAR e o transistor Q2 LIGAR. Portanto, o transistor Q2 não entrará em saturação. Portanto, fará com que a saída VOUT1 seja puxada para o valor HIGH e o valor da saída VOUT2 seja baixo devido à queda na resistência R2.

Vamos ver como o transistor Q1 e Q2 liga e desliga quando uma tensão é aplicada.

Os dois transistores como Q1 e Q2 neste circuito são conectados como um amplificador diferencial por um resistor emissor comum.

As fontes de tensão para este circuito de exemplo são VCC = 5,0, VBB = 4,0 e VEE = 0 V. Os valores de nível ALTO e BAIXO de entrada são simplesmente definidos como 4,4 V e 3,6 V. Na verdade, este circuito gera níveis de saída LOW & HIGH que são 0,6 Volts mais altos; no entanto, isso é corrigido em circuitos ECL reais.

Uma vez que Vin é HIGH, então o transistor Q1 é ligado, porém não saturado e o transistor Q2 é desligado. Assim, a tensão de saída como VOUT2 é puxada para 5 V através do resistor R2 e pode-se mostrar que a queda de tensão no resistor R1 é de cerca de 0,8 V, de modo que VOUT1 = 4,2 V (LOW). Além disso, VE = VOUT1 – VQ1 => 4,2 V – 0,4 V = 3,8 V, pois o transistor Q1 é completamente ligado.

Uma vez que Vin estiver em BAIXO, o transistor Q2 será ligado, mas não saturado e o transistor Q1 será desligado. Portanto, VOUT1 é puxado para 5,0 V usando um resistor R1 e pode ser mostrado que VOUT2 é 4,2 V. Também VE => VOUT2 – VQ2 => 4,2 V – 0,8 V => 3,4 V quando o transistor Q2 é ligado.

Em ECL, os dois transistores nunca estão em saturação, pois t As oscilações de tensão de entrada / saída são bastante pequenas, como 0,8 v e a impedância de entrada é alta e a resistência de saída é baixa. Isso ajuda a ECL a operar mais rapidamente com menos tempo de atraso de propagação.

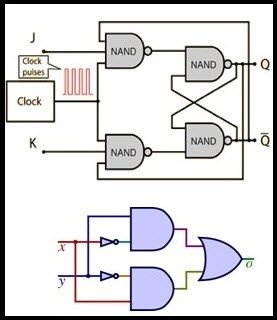

Circuito lógico de porta OU/NOR acoplado a emissor de duas entradas

O circuito da porta OR/NOR da lógica acoplada ao emissor de duas entradas é mostrado abaixo. Este circuito é projetado modificando o circuito inversor acima. A modificação é adicionando um transistor extra no lado da entrada.

O funcionamento deste circuito é muito simples. Quando as entradas aplicadas nos transistores Q1 e Q2 estiverem baixas, a saída1 (Vout1) será um valor ALTO. Assim, este Vout1 corresponde à saída da porta NOR.

Simultaneamente, se o transistor Q3 estiver ligado, ele fará com que a segunda saída (Vout2) seja HIGH. Assim, esta saída Vou2 corresponde à saída da porta OR.

Da mesma forma, se ambas as entradas dos transistores Q1 e Q2 forem HIGH, ele ligará os transistores Q1 e Q2 e fornecerá a saída baixa no terminal VOUT1.

Se o transistor Q3 estiver desligado durante esta operação, ele fornecerá alta saída no terminal VOUT2. Assim, a tabela verdade para a porta OR/NOR é dada abaixo.

|

Entradas |

Entradas | OU |

NEM |

|

UMA |

B | S | S |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Características da Lógica Acoplada ao Emissor

As características do ECL incluem o seguinte.

- Comparado ao TTL, o ECL tem um tempo de propagação mais rápido, variando de 0,5 a 2 ns. Mas, a dissipação de energia lógica acoplada ao emissor é maior em comparação com TTL como 30 mW.

- As tensões de E/S de ECL têm uma pequena oscilação como 0,8.

- A impedância de entrada do ECL é alta e a resistência de saída é baixa; consequentemente, o transistor muda seus estados muito rapidamente.

- A capacidade de fan-out das ECLs é alta e os atrasos de porta são baixos.

- A lógica o/p da ECL muda de um estado BAIXO para ALTO, mas os níveis de tensão para esses estados variam entre TTL e EC.

- A imunidade a ruídos do ECL é de 0,4V.

Vantagens e desvantagens

o vantagens da lógica acoplada ao emissor são discutidos abaixo.

- O fanout do ECL é 25, o que é melhor em comparação com o TTL e é baixo em comparação com o CMOS.

- O tempo médio de atraso de propagação de ECL é de 1 a 4 ns, o que é melhor em comparação com CMOS e

- TTL. Assim, é chamado de família lógica mais rápida.

- Quando os BJTs no emissor acoplados portas lógicas trabalham na região ativa, então eles têm a velocidade máxima em comparação com todas as famílias lógicas.

- As portas ECL geram saídas complementares.

- Os picos de comutação de corrente não existem nos cabos da fonte de alimentação.

- As saídas podem ser acopladas em conjunto para fornecer a função OR com fio.

- Os parâmetros de ECL não mudam muito com a temperatura.

- O não. de funções acessíveis a partir de um único chip é alto.

o Desvantagens da lógica acoplada ao emissor são discutidos abaixo.

- Tem uma margem de ruído extremamente menor, ou seja, ±200 mV.

- A dissipação de energia é alta em comparação com outras portas lógicas.

- Para interagir com outras famílias lógicas, são necessários deslocadores de nível.

- Fanout limita a carga capacitiva.

- Em comparação com TTL , as portas ECL são caras.

- Em comparação com CMOS e TTL, a imunidade ao ruído ECL é pior.

Formulários

As aplicações da lógica acoplada ao emissor incluem o seguinte.

- A lógica acoplada ao emissor é usada como uma tecnologia de lógica e interface em dispositivos de comunicação de velocidade extremamente alta, como interfaces de transceptor de fibra óptica, redes Ethernet e ATM (modo de transferência assíncrona).

- ECL é uma família lógica baseada em BJT onde sua operação de alta velocidade pode ser alcançada usando uma oscilação de tensão relativamente pequena e evitando que os transistores se movam para a região de saturação.

- ECL é usado para fazer os circuitos ASLT dentro do IBM 360/91.

- A ECL evita a utilização de transistores empilhados usando uma polarização i/p de terminação única e feedback positivo entre os transistores primário e secundário para obter uma função de inversor.

- ECL é usado em eletrônica de velocidade extremamente alta.

Assim, isso é uma visão geral de uma lógica acoplada ao emissor ou ECL – circuito, funcionamento, recursos, características e aplicações. ECL é uma família lógica muito mais rápida baseada em BJT em comparação com outras famílias lógicas digitais. Ele atinge sua operação de velocidade máxima usando uma pequena oscilação de tensão e evitando que os transistores se movam para a região de saturação. Esta família lógica fornece um atraso de propagação incrível de 1ns e nas famílias ECL mais recentes, esse atraso é reduzido. Aqui está uma pergunta para você, qual é um nome alternativo para ECL?