Dois tipos principais de FETs que existem atualmente são: JFETs e MOSFETs.

MOSFETs podem ser classificados em tipo de esgotamento e tipo de aprimoramento. Ambos os tipos definem o modo fundamental de operação dos MOSFETs, enquanto o próprio termo MOSFET é a abreviatura de transistor de efeito de campo de semicondutor de óxido metálico.

Devido ao fato de os dois tipos possuírem características de funcionamento diferentes, estaremos avaliando cada um deles separadamente em artigos diferentes.

Diferença entre MOSFET de aprimoramento e esgotamento

Basicamente, ao contrário dos MOSFETs de aprimoramento, os MOSFETs de depleção estão no estado ligado, mesmo na presença de 0 V nos terminais porta-fonte (VGS).

Para um MOSFET de aprimoramento, a tensão de porta para fonte (VGS) deve estar acima de sua tensão de limite de porta para fonte (VGS (th)) a fim de fazê-lo conduzir .

No entanto, para um MOSFET de depleção do canal N, seu valor VGS (th) é acima de 0 V. Isso significa que mesmo se VGS = 0 V, um MOSFET de depleção é capaz de conduzir corrente. Para desligá-lo, o VGS de um MOSFET de depleção precisa ser reduzido abaixo do VGS (th) (negativo).

Neste artigo, discutiremos o tipo de esgotamento MOSFET, que dizem ter características que correspondem às de um JFET. A semelhança é entre o corte e a saturação perto de IDSS.

Construção Básica

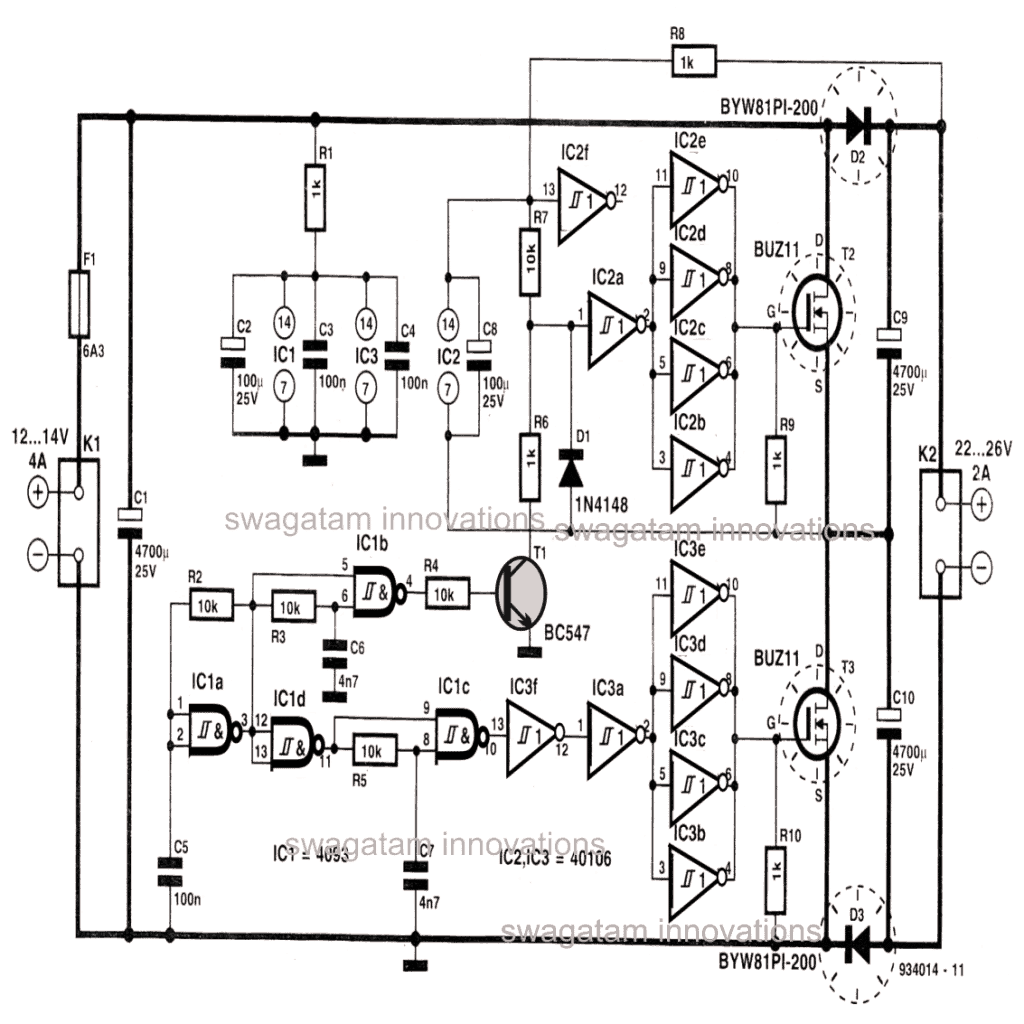

A Fig.5.23 mostra a estrutura interna básica de um MOSFET do tipo depleção de canal n.

Podemos encontrar um bloco de material tipo p criado a partir de uma base de silício. Este bloco é denominado substrato.

O substrato é a base ou fundação sobre a qual um MOSFET é construído. Para alguns MOSFETs, ele está internamente vinculado ao terminal de 'origem'. Além disso, muitos dispositivos oferecem uma saída extra na forma de SS, apresentando um MOSFET de 4 terminais, conforme revelado na Fig.5.23

O dreno e os terminais da fonte são conectados por meio de contatos condutores a locais dopados com n e conectados por meio de um canal n, conforme indicado na mesma figura.

O portão também está conectado a uma camada metálica, embora seja isolado do canal n através de uma fina camada de dióxido de silício (SiOdois)

SiOdoispossui uma forma única de propriedade de isolamento chamada dielétrico, que cria um campo elétrico oposto dentro de si em resposta a um campo elétrico aplicado externamente.

Por ser uma camada isolante, o material SiOdoisoferece-nos as seguintes informações importantes:

Um isolamento completo é desenvolvido entre o terminal do gate e o canal mosfet com este material.

Além disso, é por causa do SiOdois, a porta do mosfet é capaz de apresentar um grau extremamente alto de impedância de entrada.

Devido a esta propriedade vital de alta impedância de entrada, a corrente de porta IGé virtualmente zero amperes para qualquer configuração MOSFET polarizada em CC.

Operação Básica e Características

AS pode ser visto na Fig.5.24, a tensão de porta para fonte foi configurada em zero volts conectando os dois terminais juntos, enquanto uma tensão VDSé aplicado nos terminais de drenagem e fonte.

Com a configuração acima, o lado do dreno estabelece um potencial positivo pelos elétrons livres do canal n, junto com uma corrente equivalente através do canal JFET. Além disso, a corrente resultante VGS= 0V ainda está sendo identificado como IDSS, conforme mostrado na Fig. 5.25

Podemos ver que na Fig.5.26 a tensão da fonte da porta VGSrecebe um potencial negativo na forma de -1V.

Este potencial negativo tenta forçar os elétrons em direção ao substrato do canal p (uma vez que as cargas se repelem) e puxar buracos do substrato do canal p (uma vez que as cargas opostas se atraem).

Dependendo de quão grande é esse viés negativo VGSou seja, ocorre uma recombinação de lacunas e elétrons que resulta na redução de elétrons livres no canal n disponível para a condução. Níveis mais altos de polarização negativa resultam em taxas mais altas de recombinação.

Conseqüentemente, a corrente de drenagem é reduzida conforme a condição de polarização negativa acima é aumentada, o que é comprovado na Fig. 5.25 para VGSníveis de VGS= -1, -2 e assim por diante, até a marca de compressão de -6V.

A corrente de drenagem como resultado, juntamente com o gráfico da curva de transferência, procede exatamente como o de um JFET.

Agora, para o V positivoGSvalores, a porta positiva atrairá elétrons em excesso (portadores livres) do substrato tipo p, por conta da corrente de fuga reversa. Isso estabelecerá novos portadores por meio de colisões resultantes entre as partículas em aceleração.

Como a tensão porta-fonte tende a aumentar na taxa positiva, a corrente de dreno mostra um aumento rápido, conforme comprovado na Fig. 5.25 pelas mesmas razões discutidas acima.

A lacuna desenvolvida entre as curvas de VGS= 0V e VGS= +1 mostra distintamente o valor pelo qual a corrente aumentou devido à variação de 1 - V do VGS

Devido ao rápido aumento da corrente de drenagem, devemos ter cuidado com a classificação de corrente máxima, caso contrário, ela pode ultrapassar o limite de tensão de porta positiva.

Por exemplo, para o tipo de dispositivo representado na Fig.5.25, aplicando um VGS= + 4V faria com que a corrente de drenagem subisse para 22,2 mA, o que pode estar cruzando o limite máximo de ruptura (corrente) do dispositivo.

A condição acima mostra que o uso de uma tensão porta-fonte positiva gera um efeito intensificado na quantidade de portadoras livres no canal, ao contrário de quando VGS= 0V.

É por isso que a região de tensão da porta positiva no dreno ou nas características de transferência é geralmente conhecida como região de aprimoramento . Esta região fica entre o corte e o nível de saturação de IDSSou a região de depleção.

Resolvendo um Exemplo de Problema

Vantagens e aplicações

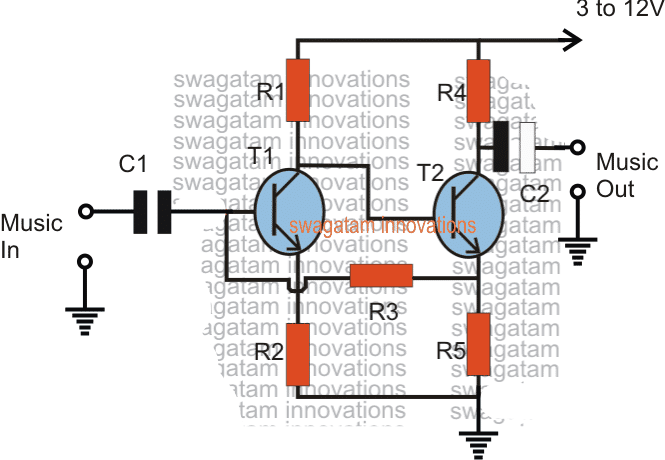

Em contraste com os MOSFETs de modo de realce, onde encontramos a corrente de dreno caindo a zero em resposta a uma tensão porta-fonte zero, o FET de modo de esgotamento moderno apresenta corrente perceptível com tensão de porta zero. Para ser preciso, a resistência do dreno à fonte é geralmente de 100 Ohms em tensão zero.

Conforme indicado no gráfico acima, a resistência ON rds(sobre)vs intervalo de sinal analógico parece uma resposta praticamente plana. Esta característica, em conjunto com os níveis de baixa capacitância desses dispositivos de esgotamento avançado, permite que sejam especificamente ideais como interruptores analógicos para aplicações de comutação de áudio e vídeo.

O atributo 'normalmente ligado' do MOSFET no modo de depleção permite que o dispositivo seja perfeitamente adequado para reguladores de corrente FET únicos.

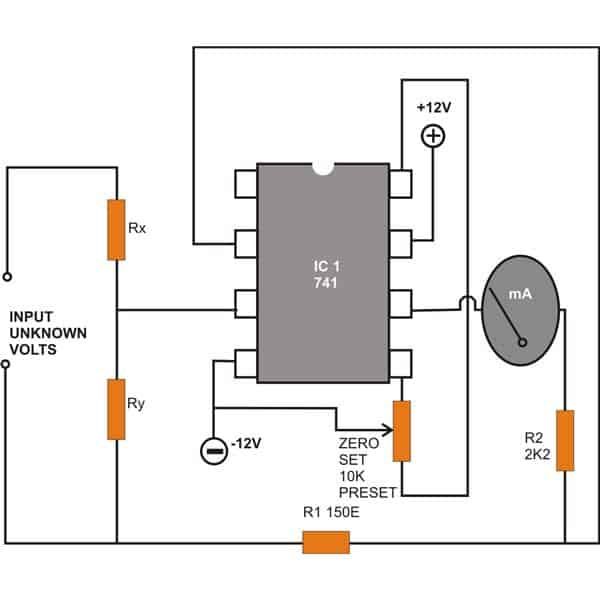

Um exemplo de circuito pode ser visto na figura a seguir.

O valor de Rs pode ser determinado usando a fórmula:

Rs= VGSdesligado[1 - (ID/EUDSS)1/2] / EUD

Onde euD é a quantidade de corrente regulada necessária na saída.

A principal vantagem dos MOSFETs no modo de depleção na aplicação de fonte de corrente é sua capacitância de drenagem mínima, o que os torna apropriados para aplicações de polarização em circuitos de vazamento de entrada baixa e velocidade média (> 50 V / us).

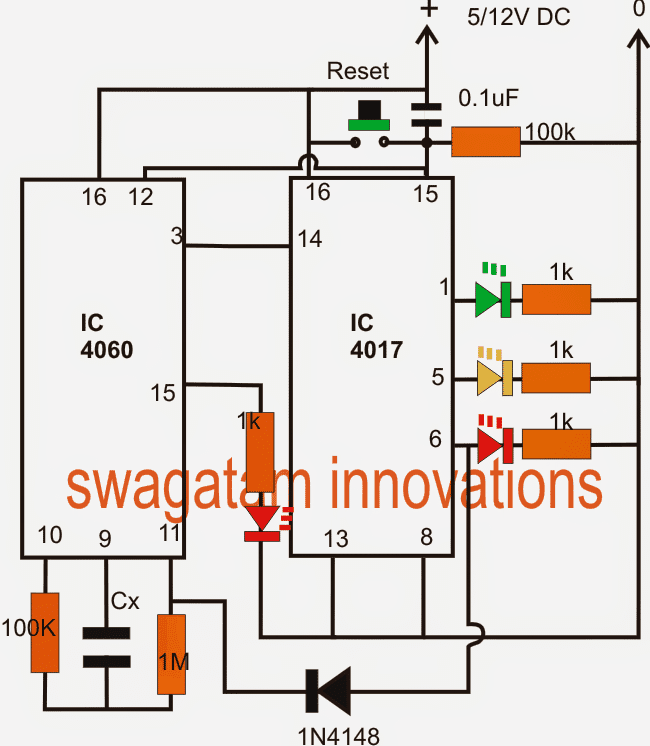

A figura abaixo exibe um diferencial de corrente diferencial de baixa entrada usando uma função dupla de baixa fuga FET.

De modo geral, qualquer lado do JFET será polarizado em ID = 500 uA. Portanto, a corrente obtida para compensação de carga e capacitâncias parasitas torna-se restrita a 2ID ou, em casos como este, 1,0 mA. Os recursos correspondentes do JFET são comprovados em produção e garantidos na folha de dados.

Cs simboliza a capacitância de saída da fonte de corrente 'cauda' do estágio de entrada. Essa capacitância é crucial em amplificadores não inversores, devido ao fato de que o estágio de entrada experimenta trocas de sinal significativas em toda a rede, e as correntes de carga em Cs podem ser grandes. No caso de fontes de corrente normais serem empregadas, esta capacitância de cauda pode ser responsável pela deterioração da taxa de variação perceptível em circuitos não inversores (em comparação com aplicações inversoras, onde as correntes de carga em Cs tendem a ser mínimas).

A queda na taxa de variação pode ser expressa como:

1 / 1+ (Cs / Sc)

Desde que Cs seja menor que Cc (o capacitor de compensação), dificilmente haverá qualquer variação na taxa de variação. Trabalhando com o DMOS FET, Cs pode ser em torno de 2 pF. Essa estratégia produz uma grande melhoria na taxa de variação. Onde déficits de corrente superiores a 1 a 5 mA são necessários, o dispositivo pode ser polarizado no modo de aprimoramento para gerar até 20 mA para um VGS máximo de +2,5 V, com a capacitância de saída mínima continuando a ser um aspecto chave.

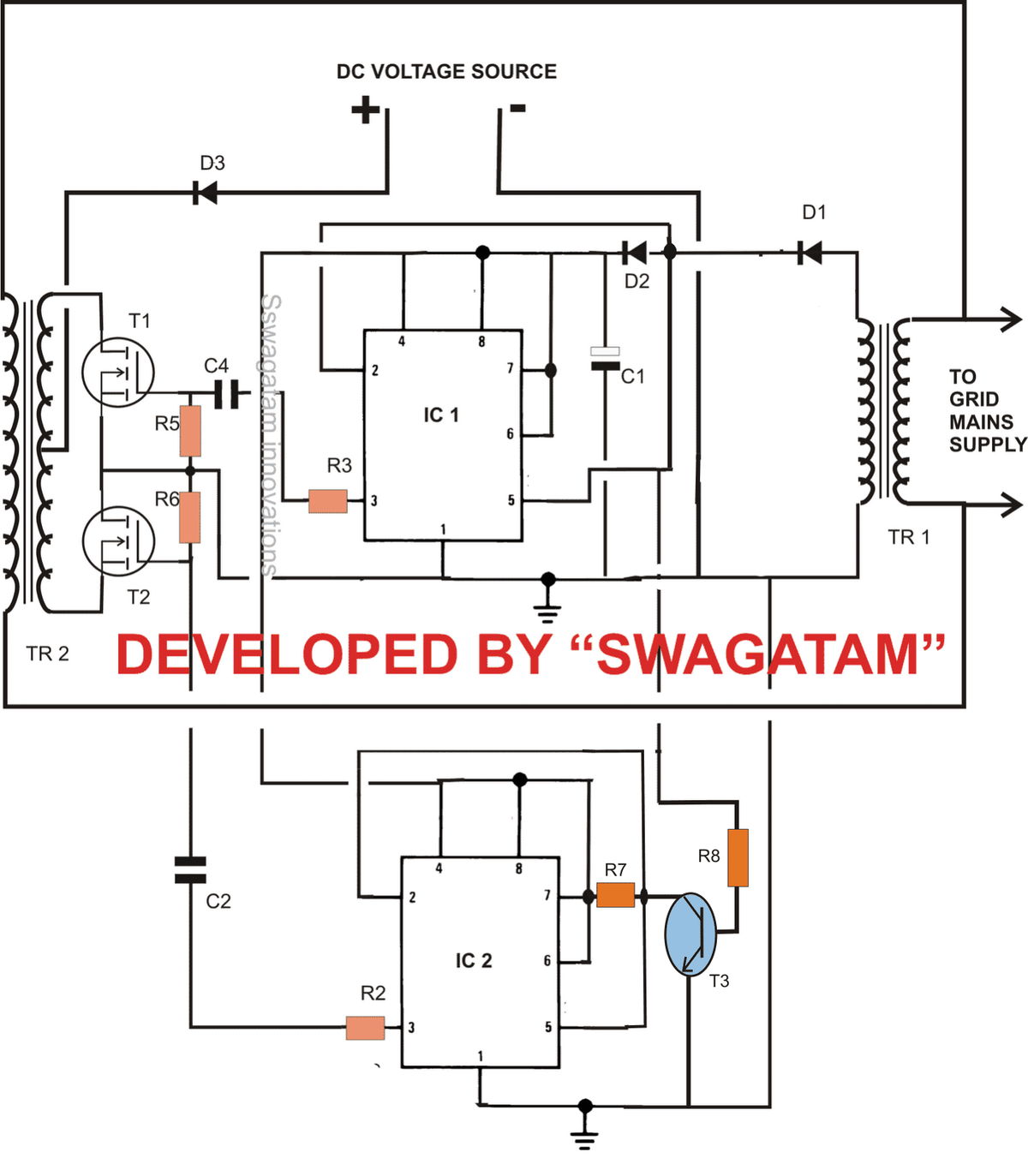

A próxima aplicação abaixo exibe um circuito de fonte de corrente de modo de aprimoramento adequado.

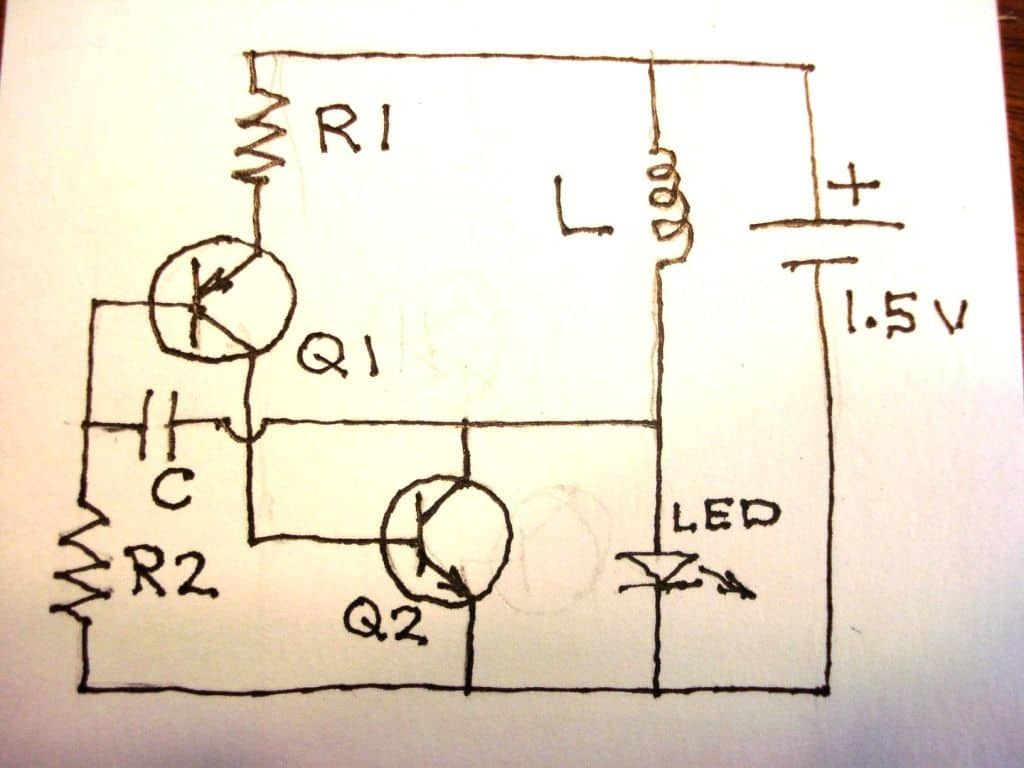

Uma chave analógica 'normalmente ligada' pode ser construída para requisitos onde a condição padrão torna-se necessária durante uma falha de tensão de alimentação, por exemplo, na faixa automática de ferramentas de teste ou para garantir a inicialização precisa de circuitos lógicos na chave ON.

A tensão de limite negativa reduzida do dispositivo oferece os pré-requisitos básicos do inversor e permite trabalhar com tensão mínima.

O circuito abaixo demonstra os fatores de polarização comuns para qualquer switch analógico DMOS de modo de depleção.

Para fazer com que o dispositivo desligue, uma voltagem negativa torna-se necessária na porta. Dito isto, a resistência ligada pode ser minimizada quando o FET é adicionalmente aumentado usando uma tensão de porta positiva, permitindo-o especificamente na região de modo de intensificação junto com a região de modo de depleção.

Essa resposta pode ser testemunhada no gráfico a seguir.

O ganho de alta frequência da unidade, junto com seus baixos valores de capacitância, oferece uma 'figura de mérito' aumentada. É realmente um elemento crucial na amplificação VHF e UHF, que especifica o produto ganho-largura de banda (GBW) do FET, que pode ser descrito como:

GBW = gfs / 2 Pi (Cno+ CFora)

MOSFET do tipo de esgotamento do canal p

A construção de um MOSFET do tipo de depleção do canal p é um reverso perfeito de uma versão do canal n mostrada na Fig.5.23. Ou seja, o substrato agora assume a forma de um tipo n e o canal se torna um tipo p, como pode ser visto na Fig. 5.28a abaixo.

A identificação do terminal permanece inalterada, mas as polaridades da tensão e da corrente estão invertidas, conforme indicado na mesma figura. As características do dreno seriam exatamente como representadas na Fig. 5.25, exceto VDSsinal que neste caso obterá um valor negativo.

A corrente de drenagem IDmostra uma polaridade positiva também neste caso, porque já invertemos sua direção. VGSmostra uma polaridade oposta, que é compreensível, conforme indicado na Fig. 5.28c.

Porque VGSé invertido produz uma imagem espelhada para as características de transferência, conforme indicado na Fig.5, 28b.

Ou seja, a corrente de dreno aumenta no V positivoGSregião do ponto de corte em VGS= Vp até IDSS, então ele continua a aumentar como o valor negativo de VGSsobe.

Símbolos

Os sinais gráficos para um MOSFET do tipo depleção dos canais n e p podem ser testemunhados na Fig. 5.29 acima.

Observe a forma como os símbolos selecionados visam representar a verdadeira estrutura do dispositivo.

A ausência de uma interconexão direta (devido ao isolamento da porta) entre a porta e o canal é simbolizada por uma lacuna entre a porta e os diferentes terminais do símbolo.

A linha vertical que representa o canal é fixada entre o dreno e a fonte e é “mantida” pelo substrato.

Dois grupos de símbolos são fornecidos na figura acima para cada tipo de canal para destacar o fato de que em alguns dispositivos o substrato pode ser acessível externamente, enquanto em outros isso pode não ser visto.

MOSFET (tipo de aprimoramento)

Embora os MOSFETs do tipo de depleção e do tipo de aprimoramento sejam semelhantes em suas estruturas internas e modo funcional, suas características podem ser bastante diferentes.

A principal diferença é a corrente de dreno que depende de um nível específico de tensão porta-fonte para a ação de corte.

Precisamente, um MOSFET do tipo de realce de canal n pode funcionar com uma tensão de porta / fonte positiva, em vez de uma gama de potenciais negativos que normalmente podem impactar um MOSFET do tipo de depleção.

Construção Básica

Você pode visualizar o MOSFET do tipo de aprimoramento de canal n na seguinte

Fig. 5.31.

Uma seção de material do tipo p é criada por meio de uma base de silício e, conforme aprendido antes, é denominada substrato.

Este substrato em algumas ocasiões é conectado internamente com o pino de origem em um MOSFET do tipo depleção, enquanto em alguns casos ele é terminado como um quarto condutor para permitir um controle externo de seu nível potencial.

Os terminais de fonte e dreno são normalmente unidos usando contatos metálicos para regiões dopadas com n.

No entanto, pode ser importante visualizar que na Fig. 5.31 o canal entre as duas regiões n-dopadas está faltando.

Isso pode ser considerado como a diferença fundamental entre o layout interno de um MOSFET do tipo de depleção e do tipo de realce, ou seja, a ausência de um canal inerente que é suposto fazer parte do dispositivo.

A camada de SiO2 pode ser vista ainda predominante, o que garante um isolamento entre a base metálica do terminal da porta e a região entre o dreno e a fonte. No entanto, aqui pode ser testemunhado estando separado da seção de material tipo p.

A partir da discussão acima, podemos concluir que um layout interno de MOSFET de depleção e aprimoramento pode ter algumas semelhanças, exceto o canal ausente entre dreno / fonte para um tipo de aprimoramento de MOSFET.

Operação Básica e Características

Para um tipo de aprimoramento MOSFET quando um 0 V é introduzido em seu VGS, devido ao canal n ausente (que é conhecido por transportar muitas portadoras livres) faz com que uma saída de corrente seja zero, o que é bastante diferente de um tipo de esgotamento de MOSFET, com ID = IDSS.

Em tal situação, devido à falta de um caminho nos terminais de dreno / fonte, grandes quantidades de portadores na forma de elétrons são incapazes de se acumular no dreno / fonte (por causa das regiões n-dopadas).

Aplicando algum potencial positivo em VDS, com VGS definido em zero volts e o terminal SS em curto com o terminal de origem, na verdade encontramos um par de junções pn polarizadas reversamente entre as regiões dopadas com n e o substrato p para permitir qualquer condução notável através drene para a fonte.

Na Fig. 5.32 mostra uma condição onde VDS e VGS são aplicados com alguma tensão positiva maior que 0 V, permitindo que o dreno e a porta estejam em um potencial positivo em relação à fonte.

O potencial positivo na porta empurra os orifícios no substrato-p ao longo da borda da camada de SiO2 saindo do local e entrando mais profundamente nas regiões do substrato-p, como mostrado na figura acima. Isso acontece por causa das cargas semelhantes que se repelem.

Isso resulta na criação de uma região de depleção próxima à camada isolante de SiO2, sem orifícios.

Apesar disso, os elétrons do p-substrato que são os portadores minoritários do material são puxados em direção ao portão positivo e começam a se reunir na região próxima à superfície da camada de SiO2.

Devido à propriedade de isolamento da camada de SiO2, os portadores negativos permitem que os portadores negativos sejam absorvidos no terminal da porta.

Conforme aumentamos o nível de VGS, a densidade de elétrons perto da superfície de SiO2 também aumenta, até que finalmente a região induzida do tipo n é capaz de permitir uma condução quantificável através do dreno / fonte.

A magnitude VGS que causa um aumento ideal na corrente de drenagem é denominada como a tensão de limiar, significado pelo símbolo VT . Nas fichas de dados, você poderá ver isso como VGS (Th).

Conforme aprendido acima, devido à ausência de um canal em VGS = 0, e 'aprimorado' com a aplicação de tensão porta-fonte positiva, este tipo de MOSFET são conhecidos como MOSFETs do tipo aprimoramento.

Você vai descobrir que ambos os MOSFETs do tipo depleção e aprimoramento exibem regiões do tipo aprimoramento, mas o termo Aprimoramento é usado para o último porque funciona especificamente usando um modo de operação aprimorado.

Agora, quando o VGS é empurrado para além do valor limite, a concentração das portadoras livres aumentará no canal onde é induzida. Isso faz com que a corrente de drenagem aumente.

Por outro lado, se mantivermos o VGS constante e aumentarmos o nível de VDS (tensão dreno para fonte), isso acabará fazendo com que o MOSFET alcance seu ponto de saturação, como normalmente também aconteceria com qualquer JFET ou um MOSFET de depleção.

Conforme mostrado na Fig. 5.33, o ID da corrente de dreno é nivelado com o auxílio de um processo de pinçamento, indicado pelo canal mais estreito em direção à extremidade do dreno do canal induzido.

Aplicando a lei de tensão de Kirchhoff às tensões terminais do MOSFET na Fig. 5.33, obtemos:

Se VGS for mantido constante para um valor específico, por exemplo 8 V, e VDS for aumentado de 2 para 5 V, a tensão VDG pela Eq. 5.11 pode ser visto caindo de -6 para -3 V, e o potencial da porta ficando cada vez menos positivo em relação à tensão de dreno.

Esta resposta proíbe que os portadores livres ou elétrons sejam puxados para esta região do canal induzido, o que por sua vez resulta em uma queda na largura efetiva do canal.

Em última análise, a largura do canal diminui até o ponto de pinch-off, atingindo uma condição de saturação semelhante ao que já aprendemos em nosso artigo anterior do MOSFET de depleção.

Ou seja, aumentar ainda mais o VDS com um VGS fixo não afeta o nível de saturação do ID, até o ponto em que uma situação de ruptura é atingida.

Olhando para a Fig 5.34, podemos identificar que para um MOSFET como na Fig.5.33 tendo VGS = 8 V, a saturação ocorre a um nível VDS de 6 V. Para ser preciso, o nível de saturação VDS está associado ao nível VGS aplicado por:

Sem dúvida, isso implica que quando o valor de VT é fixo, o aumento do nível de VGS causará, proporcionalmente, níveis mais elevados de saturação para VDS através do locus dos níveis de saturação.

Referindo-se às características mostradas na figura acima, o nível de VT é 2 V, o que é evidente pelo fato de que a corrente de dreno caiu para 0 mA.

Portanto, normalmente podemos dizer:

Quando os valores de VGS são menores que o nível de limite para MOSFET do tipo aprimoramento, sua corrente de drenagem é 0 mA.

Também podemos ver claramente na figura acima que, enquanto o VGS é elevado de VT para 8 V, o nível de saturação correspondente para ID também aumenta de 0 a 10 mA.

Além disso, podemos ainda notar que o espaço entre os níveis de VGS aumenta com o aumento do valor de VGS, causando um aumento infinito na corrente de dreno.

Descobrimos que o valor da corrente de drenagem está relacionado à tensão porta-fonte para níveis VGS que são maiores do que VT, por meio da seguinte relação não linear:

O termo que é mostrado entre colchetes é o termo responsável pela relação não linear entre ID e VGS.

O termo k é uma constante e é uma função do layout do MOSFET.

Podemos descobrir o valor desta constante k através da seguinte equação:

onde o ID (ativado) e o VGD (ativado) são valores que dependem especificamente da característica do dispositivo.

Na próxima Fig. 5.35 abaixo, encontramos as características de drenagem e transferência dispostas uma ao lado da outra para esclarecer o processo de transferência entre si.

Basicamente, é semelhante ao processo explicado anteriormente para JFET e MOSFETs do tipo depleção.

No entanto, para o caso presente, devemos lembrar que a corrente de dreno é de 0 mA para VGS VT.

Aqui, o ID pode ver uma quantidade perceptível de corrente, que aumentará conforme determinado pela Eq. 5,13.

Observe que ao definir os pontos sobre as características de transferência das características do dreno, consideramos apenas os níveis de saturação. Isso restringe a região de operação a valores VDS maiores do que os níveis de saturação estabelecidos pela Eq. (5,12).

MOSFETs do tipo p-Channel Enhancement

A estrutura de um MOSFET do tipo de intensificação do canal p, conforme mostrado na Fig. 5.37a, é exatamente o oposto do mostrado na Fig. 5.31.

Ou seja, agora você descobre que um substrato do tipo n e regiões dopadas com p sob o dreno e as juntas de origem.

Os terminais continuam conforme estabelecidos, mas cada uma das direções da corrente e as polaridades da tensão são invertidas.

As características do dreno podem ser semelhantes às mostradas na Fig. 5.37c, tendo quantidades crescentes de corrente causadas por magnitudes continuamente mais negativas de VGS.

As características de transferência seriam a impressão espelhada (em torno do eixo do ID) da curva de transferência da Fig. 5.35, tendo o ID aumentando com mais e mais valores negativos de VGS acima do VT, conforme mostrado na Fig. 5.37b. As Equações (5.11) a (5.14) são igualmente apropriadas para dispositivos de canal p.

Referências:

- https://en.wikipedia.org/wiki/MOSFET

- https://hi.wikipedia.org/wiki/%E0%A4%AE%E0%A5%89%E0%A4%B8%E0%A4%AB%E0%A5%87%E0%A4%9F

Anterior: Circuito Detector Anti Spy RF - Detector de insetos sem fio Próximo: Características de transferência