Conjunto de instruções ou arquitetura de conjunto de instruções é a estrutura do computador que fornece comandos ao computador para guiá-lo no processamento da manipulação de dados. O conjunto de instruções consiste em instruções, modos de endereçamento, tipos de dados nativos, registros, interrupção, tratamento de exceções e arquitetura de memória. O conjunto de instruções pode ser emulado no software usando um intérprete ou embutido no hardware do processador. A arquitetura do conjunto de instruções pode ser considerada como um limite entre o software e o hardware. Classificação de microcontroladores e os microprocessadores podem ser feitos com base na arquitetura de conjunto de instruções RISC e CISC.

Conjunto de instruções do processador

O conjunto de instruções especifica a funcionalidade do processador, incluindo as operações suportadas pelo processador, os mecanismos de armazenamento do processador e a maneira de compilar os programas para o processador.

O que é RISC e CISC?

O RISC e CISC pode ser expandido da seguinte forma:

RISC representa o Computador de Conjunto de Instruções Reduzidas e

CISC representa o computador do conjunto de instruções complexas.

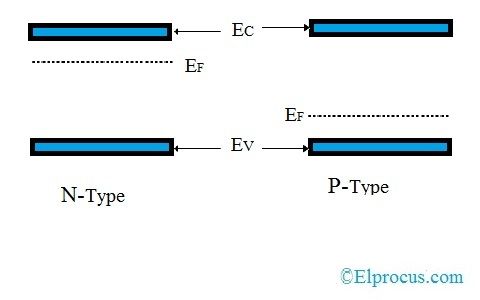

Arquitetura RISC (Reduced Instruction Set Computer)

Arquitetura RISC

O arquitetura de microcontrolador que utiliza um conjunto pequeno e altamente otimizado de instruções é denominado computador de conjunto de instruções reduzido ou simplesmente denominado RISC. É também chamada de arquitetura LOAD / STORE.

No final dos anos 1970 e no início dos anos 1980, os projetos RISC foram desenvolvidos principalmente em Stanford, UC-Berkley e IBM. A equipe de pesquisa John Coke da IBM desenvolveu o RISC reduzindo o número de instruções necessárias para processar cálculos mais rápido do que o CISC. A arquitetura RISC é mais rápida e os chips necessários para a fabricação da arquitetura RISC também são mais baratos em comparação com a arquitetura CISC.

Características típicas da arquitetura RISC

- A técnica de pipelining do RISC executa várias partes ou estágios de instruções simultaneamente, de modo que todas as instruções na CPU sejam otimizadas. Conseqüentemente, os processadores RISC têm Clock por Instrução de um ciclo, e isso é chamado de Execução de Um Ciclo.

- Otimiza o uso de registro com mais número de registros no RISC e mais número de interações dentro da memória podem ser evitados.

- Modos de endereçamento simples, até mesmo endereçamento complexo pode ser feito usando aritmética E / OU operações lógicas .

- Ele simplifica o projeto do compilador usando registradores de propósito geral idênticos, o que permite que qualquer registrador seja usado em qualquer contexto.

- Para o uso eficiente dos registros e otimização dos usos de pipelining, é necessário um conjunto reduzido de instruções.

- O número de bits usados para o opcode é reduzido.

- Em geral, existem 32 ou mais registros no RISC.

Vantagens da arquitetura do processador RISC

- Devido ao pequeno conjunto de instruções do RISC, os compiladores de linguagem de alto nível podem produzir um código mais eficiente.

- RISC permite a liberdade de usar o espaço em microprocessadores por causa de sua simplicidade.

- Em vez de usar Stack, muitos processadores RISC usam os registradores para passar argumentos e manter as variáveis locais.

- As funções RISC usam apenas alguns parâmetros e os processadores RISC não podem usar as instruções de chamada e, portanto, usam instruções de comprimento fixo que são fáceis de pipeline.

- A velocidade da operação pode ser maximizada e o tempo de execução pode ser minimizado.

- São necessários muito menos formatos de instrução (menos de quatro), um pequeno número de instruções (cerca de 150) e alguns modos de endereçamento (menos de quatro).

Desvantagens da arquitetura do processador RISC

- Com o aumento do comprimento das instruções, aumenta a complexidade para os processadores RISC executarem devido ao seu ciclo de caracteres por instrução.

- O desempenho dos processadores RISC depende principalmente do compilador ou programador, pois o conhecimento do compilador desempenha um papel importante ao converter o código CISC em um código RISC, portanto, a qualidade do código gerado depende do compilador.

- Ao reprogramar o código CISC para um código RISC, denominado como uma expansão de código, o tamanho aumentará. E, a qualidade desta expansão de código dependerá novamente do compilador, e também do conjunto de instruções da máquina.

- O cache de primeiro nível dos processadores RISC também é uma desvantagem do RISC, em que esses processadores têm grandes caches de memória no próprio chip. Para alimentar as instruções, eles exigem muito sistemas de memória rápidos .

Arquitetura CISC (Complex Instruction Set Computer)

O principal objetivo da arquitetura do processador CISC é completar a tarefa usando menos número de linhas de montagem. Para isso, o processador é construído para executar uma série de operações. A instrução complexa também é denominada como MULT, que opera bancos de memória de um computador diretamente, sem fazer com que o compilador execute funções de armazenamento e carregamento.

CISC Architecture

Características da arquitetura CISC

- Para simplificar a arquitetura do computador, o CISC oferece suporte à microprogramação.

- O CISC tem mais instruções predefinidas, o que torna as linguagens de alto nível fáceis de projetar e implementar.

- CISC consiste em menos número de registros e mais número de modos de endereçamento, geralmente de 5 a 20.

- O processador CISC leva vários tempos de ciclo para a execução das instruções - ciclos de vários relógios.

- Por causa do complexo conjunto de instruções do CISC, a técnica de pipelining é muito difícil.

- CISC consiste em mais número de instruções, geralmente de 100 a 250.

- Instruções especiais são usadas muito raramente.

- Operandos na memória são manipulados por instruções.

Vantagens da arquitetura CISC

- Cada instrução de linguagem de máquina é agrupada em uma instrução de microcódigo e executada de acordo, e então são armazenadas embutidas na memória do processador principal, denominado como implementação de microcódigo.

- Como a memória do microcódigo é mais rápida do que a memória principal, o conjunto de instruções do microcódigo pode ser implementado sem redução considerável de velocidade sobre a implementação com fio.

- Todo o novo conjunto de instruções pode ser manipulado modificando o design do microprograma.

- CISC, o número de instruções necessárias para implementar um programa pode ser reduzido pela construção de conjuntos de instruções ricos e também pode ser feito para usar a memória principal lenta de forma mais eficiente.

- Por causa do superconjunto de instruções que consiste em todas as instruções anteriores, isso facilita a micro codificação.

Desvantagens do CISC

- A quantidade de tempo gasto por instruções diferentes será diferente - devido a isso - o desempenho da máquina fica mais lento.

- A complexidade do conjunto de instruções e o hardware do chip aumentam à medida que cada nova versão do processador consiste em um subconjunto de gerações anteriores.

- Apenas 20% das instruções existentes são usadas em um evento de programação típico, embora existam muitas instruções especializadas que nem mesmo são usadas com frequência.

- Os códigos condicionais são configurados pelas instruções CISC como um efeito colateral de cada instrução que leva tempo para esta configuração - e, como a instrução subsequente altera os bits do código de condição - então, o compilador deve examinar os bits do código de condição antes que isso aconteça.

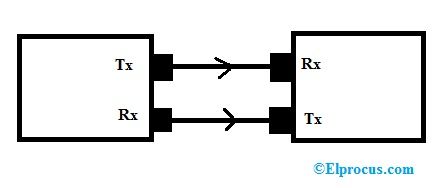

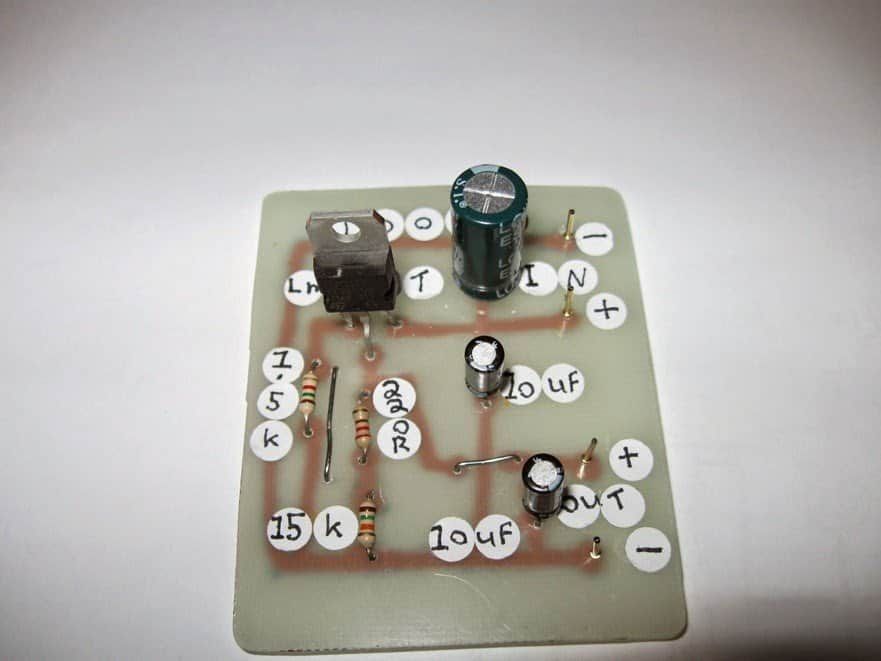

RISC vs. CISC

- Os ciclos de desperdício podem ser evitados pelo programador removendo o código desnecessário no RISC, mas, ao usar o código CISC, leva a ciclos de desperdício devido à ineficiência do CISC.

- No RISC, cada instrução se destina a realizar uma pequena tarefa, de forma que, para realizar uma tarefa complexa, várias pequenas instruções são usadas juntas, enquanto apenas algumas instruções são necessárias para fazer a mesma tarefa usando CISC - pois é capaz de realizar tarefas complexas como as instruções são semelhantes a um código de alta linguagem.

- CISC é normalmente usado para computadores, enquanto RISC é usado para smartphones, tablets e outros dispositivos eletrônicos.

A figura a seguir mostra mais diferenças entre RISC e CISC

RISC vs. CISC

Portanto, este artigo discute sobre os recursos das arquiteturas RISC e CISC das vantagens e desvantagens da arquitetura dos processadores RISC e CISC do RISC e CISC, e as diferenças entre as arquiteturas RISC e CISC com uma breve ideia. Para obter mais informações sobre as arquiteturas RISC e CISC, poste suas dúvidas comentando abaixo.

Créditos fotográficos:

- Conjunto de instruções do processador por arstechnica

- Arquitetura RISC por lsi-contest

- RISC vs. CISC por csarassignment