O post discute a função de pinagem e outras especificações importantes do IC 4043. Vamos aprender sobre o datasheet completo deste chip muito interessante.

Folha de dados de pinagem de IC 4043

Tecnicamente, o IC 4043 é um trinco set / reset (R / S) quádruplo com saída de 3 estados lógicos.

Para ser mais preciso, este chip tem 4 conjuntos de entradas (significando 8 pinagens de entrada) e 4 saídas únicas correspondentes.

Os 4 conjuntos de entradas consistem em 4 pares de entradas de definir / redefinir.

Para cada set / reset, temos uma saída correspondente.

Todas essas entradas de reset ajustadas respondem a sinais lógicos altos, criando um efeito biestável em suas pinagens de saída correspondentes.

Flip / Flop biestável

Biestável refere-se à ação de flip-flop, em outras palavras, um pulso alto para a entrada 'set' torna a saída correspondente alta de seu estado original baixo, e um alto para a entrada de reset reverte o estado acima de alto para baixo.

Portanto, basicamente para tornar as saídas correspondentes altas, precisamos aplicar um alto em suas entradas 'configuradas' e para tornar as saídas baixas novamente, simplesmente precisamos aplicar outro alto em suas entradas de reset.

O funcionamento das pinagens de entrada e saída são simples assim.

Além disso, o IC tem outra pinagem de entrada interessante OE, que é uma pinagem de habilitação de saída comum.

Definir / Reiniciar Função

Para ativar as ações de ajuste / redefinição explicadas acima no IC, esta entrada OE deve ser conectada com lógica alta ou simplesmente com Vdd (alimentação de energia).

Na situação acima, a saída é permitida com o funcionamento do flip-flop especificado.

Se a entrada OE estiver conectada ao terra, a saída congela e produz uma resposta de alta impedância, que não mostra uma saída baixa nem uma alta, em vez disso, bloqueia a entrada em um estado bloqueado sem resposta, daí o nome 3 saída de estado lógico.

Assim, a entrada OE pode ser usada para desligar o funcionamento do IC se necessário para uma aplicação específica.

O IC funciona melhor com tensões de alimentação de 5 a 15V.

Vamos resumir as funções de pinagem de entrada e saída e especificações do IC 4043 com os seguintes dados:

- 1Q a 4Q (pinos: 2, 9, 10, 1) saída de trava com buffer de 3 estados

- 1R a 4R (pinos: 3, 7, 11, 15) entrada de reset (ativo HIGH)

- 1S a 4S (pinos: 4, 6, 12, 14) definir entrada (HIGH ativo)

- OE (Pin: 5) entrada de habilitação de saída comum

- VSS (Pin: 8) tensão de alimentação de aterramento

- N.C. (Pin: 13) não conectado

- Tensão de alimentação VDD (Pin: 16)

Mais atualizações:

Nestes posts tentamos entender o funcionamento do IC 4043 e IC 4044 estudando as várias especificações, datasheet dos dispositivos e sua disposição de pinagem.

Basicamente, ambas as variantes são R / S de estado 4 CMOS de acoplamento cruzado quádruplo ou travas de reinicialização / definição. Quad significa ter 4 saídas que podem ser definidas ou travadas com uma lógica alta por meio de um sinal de entrada de controle ou redefinidas para zero lógico por um sinal de entrada subsequente.

O recurso de 3 estados permite que os ICs sejam controlados usando 3 lógicas

O princípio de funcionamento básico de IC 4043 e IC 4044 é o mesmo que acima, sendo a única diferença, IC 4043B são quad cross-coupled de 3 estados NEM Latch, e IC 4044B são quad cross-coupled 3-state NAND Robusto.

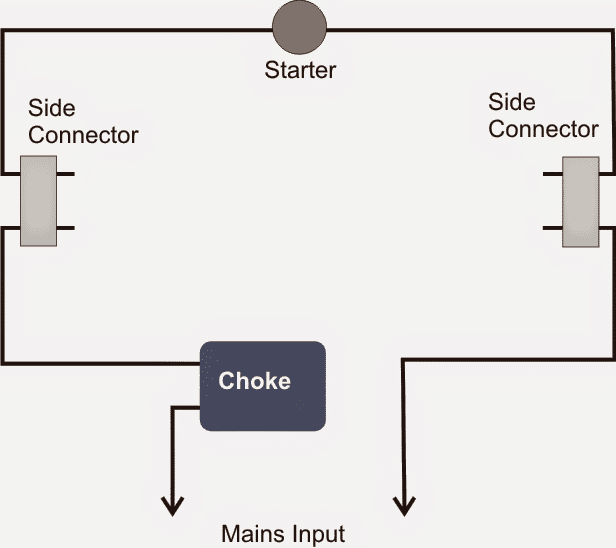

Diagrama de Pinagem

Os seguintes diagramas de pinagem dos ICs mostram a estrutura interna e detalhes de pinagem dos dispositivos:

Nos diagramas acima, podemos ver que cada um dos tipos possui 4 travas com uma saída e 2 entradas RESET / SET individuais. A função do pino ENABLE para todas as entradas SET / RESET é idêntica.

Uma lógica HIGH no pino ENABLE permite que os estados de trava sejam conectados às saídas relevantes, uma lógica baixa ou 0 desconecta os estados de trava de suas saídas, causando um circuito aberto completo nas saídas.

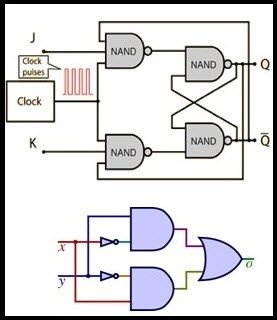

Trava NOR, Diagramas lógicos equivalentes de trava NAND

Os diagramas a seguir mostram as travas equivalentes na forma de travas NOR e NAND, que estão presentes dentro de cada uma das 4 travas dos ICs individuais.

Como podemos ver, cada um dos blocos de trava são controlados usando 3 entradas de controle lógico, nomeadamente SET, RESET e ENABLE, portanto, a saída é dependente desses 3 estados de entrada. A tabela verdade para esses 3 estados lógicos pode ser aprendida no diagrama a seguir:

Na tabela verdade acima, a forma completa dos vários alfabetos simbólicos abreviados pode ser entendida como dada abaixo: S = SET Pino R = RESET Pino E = ATIVAR Pino Q = SAÍDA Pino OC = Circuito aberto NC = Sem alteração

As principais características do IC 4043 e IC 4044 estão resumidas abaixo:

Simulação prática básica de trabalho dos pinos SET / RESET e ENABLE

Descrição de Trabalho

A partir do GIF de simulação acima, podemos entender o funcionamento dos módulos quad latch com os seguintes pontos:

Quando o pino SET é aplicado com uma alimentação positiva, a saída fica alta e se torna travada mesmo se o potencial positivo for removido do pino SET, conforme indicado pelo LED vermelho (polarização direta).

Quando o pino RESET é aplicado com um pulso positivo, a trava se quebra e a saída fica BAIXA permanentemente, mesmo se o positivo for removido do pino RESET. Isso é indicado pela iluminação do LED azul.

As operações acima podem ser implementadas apenas enquanto o pino ENABLE do IC estiver com um potencial de alimentação positivo. Quando conectada a um potencial negativo ou de terra, a saída da trava se torna aberta e não responde às operações SET / RESET.

Anterior: Circuito de cronômetro programável para o dia da semana Próximo: IC 4033 Pinouts, Datasheet, Application