A unidade de controle é o principal componente de uma unidade central de processamento (CPU) em computadores que podem direcionar as operações durante a execução de um programa por o processador /computador. A principal função da unidade de controle é buscar e executar instruções da memória de um computador. Ele recebe as instruções / informações de entrada do usuário e as converte em sinais de controle , que são então fornecidos à CPU para execução posterior. Ele está incluído como parte da arquitetura Von Neumann desenvolvida por John Neumann. É responsável por fornecer os sinais de temporização, sinais de controle e direcionar a execução de um programa pela CPU. Ele é incluído como uma parte interna da CPU em computadores modernos. Este artigo descreve informações completas sobre a unidade de controle.

O que é a unidade de controle?

Componente que recebe o sinal / informação / instrução de entrada do usuário e se converte em sinais de controle para execução na CPU. Ele controla e dirige a memória principal, unidade aritmética e lógica (ALU), dispositivos de entrada e saída, e também responsável pelas instruções que são enviadas para a CPU de um computador. Ele busca as instruções do memória principal de um processador e enviado para o registro de instrução do processador, que contém o conteúdo do registro.

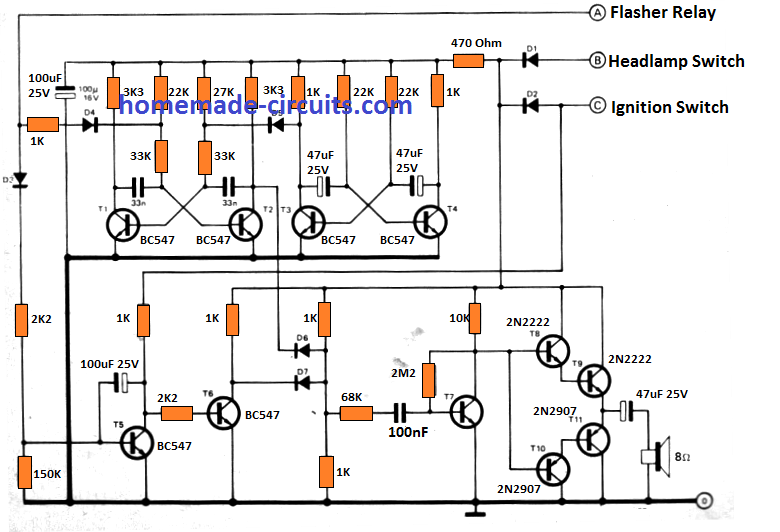

Diagrama de blocos da unidade de controle

A unidade de controle converte a entrada em sinais de controle e, em seguida, envia ao processador e direciona a execução de um programa. As operações a realizar são dirigidas pelo processador no computador. Principalmente Unidade de Processamento Central (CPU) e Unidade de Processamento Gráfico (GPU) requerem uma unidade de controle como parte interna. O diagrama de blocos da unidade de controle é mostrado acima.

Componentes de uma unidade de controle

Os componentes desta unidade são instruções registra , sinais de controle dentro da CPU, sinais de controle de / para o barramento, barramento de controle, sinalizadores de entrada e sinais de relógio.

Os componentes da unidade de controle com fio são registro de instrução (contém opcode e campo de endereço), unidade de tempo, estado de controle gerador , matriz de geração de sinal de controle e decodificador de instrução.

Os componentes da unidade de controle micro programada são o próximo gerador de endereço, um registro de endereço de controle, memória de controle e registro de dados de controle.

Funções

O funções da unidade de controle inclui o seguinte.

- Ele direciona o fluxo da sequência de dados entre o processador e outros dispositivos.

- Ele pode interpretar as instruções e controlar o fluxo de dados no processador.

- Ele gera a seqüência de sinais de controle das instruções recebidas ou comandos do registrador de instrução.

- Ele tem a responsabilidade de controlar as unidades de execução, como ALU, buffers de dados e registros na CPU de um computador.

- Ele tem a capacidade de buscar, decodificar, manipular a execução e armazenar resultados.

- Não pode processar e armazenar os dados

- Para transferir os dados, ele se comunica com os dispositivos de entrada e saída e controla todas as unidades do computador.

Projeto da Unidade de Controle

O design disso pode ser feito usando dois tipos de uma unidade de controle que incluem o seguinte.

- Baseado em hardwire

- Com base microprogramada (nível único e dois níveis)

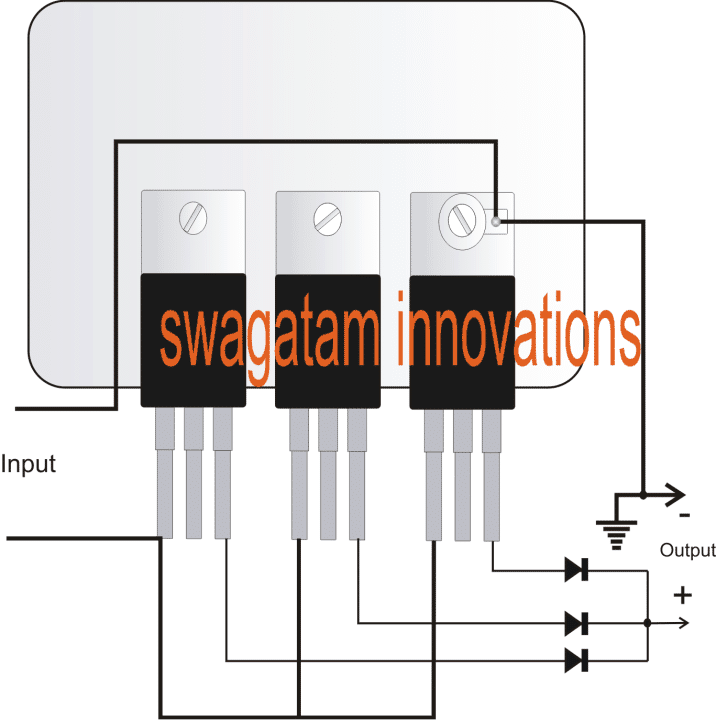

Unidade de controle com fio

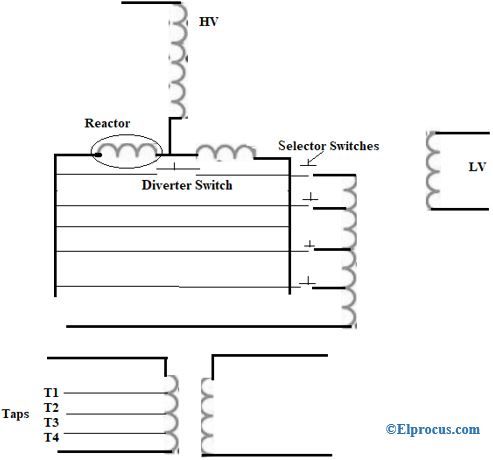

O projeto básico de uma unidade de controle com fio é mostrado acima. Neste tipo, os sinais de controle são gerados por um hardware especial circuito lógico sem qualquer mudança na estrutura do circuito. Nesse caso, o sinal gerado não pode ser modificado para execução no processador.

Os dados básicos de um opcode (código de operação de uma instrução é enviado para o decodificador de instrução para decodificação. decodificador é o conjunto de decodificadores para decodificar diferentes tipos de dados no opcode. Isso resulta em sinais de saída que contêm valores de sinais ativos que são fornecidos como entrada para o gerador de matriz para gerar sinais de controle para a execução de um programa pelo processador do computador.

Unidade de controle baseada em hardwire

O gerador de matriz fornece estados da unidade de controle e os sinais de saída do processador (sinais de interrupção). Matrix é construída como o array lógico programável . Os sinais de controle gerados pelo gerador de matriz são fornecidos como entrada para a próxima matriz do gerador e combinados com os sinais de temporização da unidade de temporização que contém padrões retangulares.

Para a busca de uma nova instrução, a unidade de controle se transforma em um estágio inicial para a execução de uma nova instrução. A unidade de controle permanece no estágio inicial ou primeiro estágio enquanto os sinais de temporização, sinais de entrada e estados de instrução de um computador permanecerem inalterados. A mudança no estado da unidade de controle pode ser elevada se houver alguma mudança em qualquer um dos sinais gerados.

Quando ocorre um sinal externo ou interrupção, a unidade de controle passa para o próximo estado e realiza o processamento do sinal de interrupção. Os sinalizadores e estados são usados para selecionar os estados desejados para realizar o ciclo de execução da instrução.

No último estado, a unidade de controle busca a próxima instrução e envia a saída para o contador do programa, então para o registrador de endereço de memória, para o registrador buffer e então para o registrador de instrução para ler a instrução. Finalmente, se a última instrução (que é buscada pela unidade de controle) é a instrução final, ela vai para o estado operacional do processador e espera até que o usuário direcione o próximo programa.

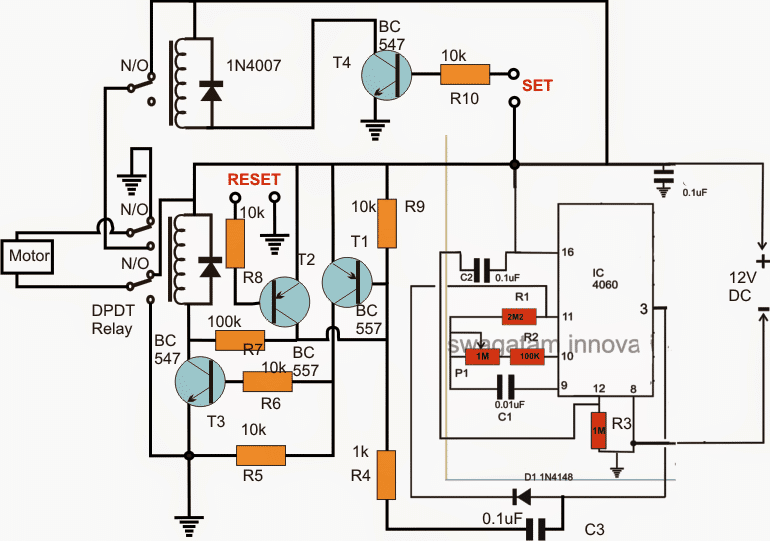

Unidade de controle microprogramada

Neste tipo, o armazenamento de controle é usado para armazenar os sinais de controle que são codificados durante a execução de um programa. O sinal de controle não é gerado imediatamente e decodificado porque o microprograma armazena o campo de endereço no armazenamento de controle. Todo o processo é um único nível.

As microoperações são feitas para a execução de microinstruções no programa. O diagrama de blocos da unidade de controle microprogramada é mostrado acima. A partir do diagrama, o endereço da microinstrução é obtido a partir do registro de endereço da memória de controle. Todas as informações da unidade de controle são armazenadas permanentemente na memória de controle chamada ROM.

Unidade de controle microprogramada

A microinstrução da memória de controle é mantida pelo registrador de controle. Como a microinstrução está na forma de palavra de controle (contém valores de controle binários), é necessário que 1 ou mais microoperações sejam realizadas para o processamento de dados.

Durante a execução das microinstruções, o próximo gerador de endereço computou o próximo endereço da microinstrução e, em seguida, envia para o registrador de endereço de controle para ler a próxima microinstrução.

A sequência de microoperações de um micro-programa é realizada pelo próximo gerador de endereço e atua como sequenciador de microprograma para obter o endereço de sequência, ou seja, ler da memória de controle.

Código Verilog para a Unidade de Controle

O código Verilog para a unidade de controle é mostrado abaixo.

`inclui“ prj_definition.v ”

módulo CONTROL_UNIT (MEM_DATA, RF_DATA_W, RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2, RF_READ, RF_WRITE, ALU_OP1, ALU_OP2, ALU_OPRN, MEM_ADDR, MEM_READ, MEM_WRITE, RF_DATA_RES_R1, CLU_DATA, RF_WRITE, ALU_OP1, ALU_OP2, ALU_OPRN, MEM_ADDR, MEM_READ, MEM_WRITE, RF_DATA_RES_R1, CLARULT2_RETA_R1, RFDAST, ZERO_RES_R1)

// Sinais de saída

// Saídas para o arquivo de registro

saída [`DATA_INDEX_LIMIT: 0] RF_DATA_W

saída [`ADDRESS_INDEX_LIMIT: 0] RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

saída RF_READ, RF_WRITE

// Saídas para ALU

saída [`DATA_INDEX_LIMIT: 0] ALU_OP1, ALU_OP2

saída [`ALU_OPRN_INDEX_LIMIT: 0] ALU_OPRN

// Saídas para a memória

saída [`ADDRESS_INDEX_LIMIT: 0] MEM_ADDR

saída MEM_READ, MEM_WRITE

// sinais de entrada

entrada [`DATA_INDEX_LIMIT: 0] RF_DATA_R1, RF_DATA_R2, ALU_RESULT

entrada ZERO, CLK, RST

// Sinal de entrada

inout [`DATA_INDEX_LIMIT: 0] MEM_DATA

// State nets

fio [2: 0] proc_state

// mantém o valor do contador do programa, armazena a instrução atual, registrador de ponteiro de pilha

reg MEM_READ, MEM_WRITE

reg MEM_ADDR

reg ALU_OP1, ALU_OP2

reg ALU_OPRN

reg RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

reg RF_DATA_W

reg [1: 0] estado, next_state

PROC_SM state_machine (.STATE (proc_state) ,. CLK (CLK) ,. RST (RST))

sempre @ (posedge CLK)

começar

if (RST)

Estado<= RST

outro

Estado<= next_state

fim

sempre @ (estado)

começar

MEM_READ = 1’b0 MEM_WRITE = 1’b0 MEM_ADDR = 1’b0

ALU_OP1 = 1’b0 ALU_OP2 = 1’b0 ALU_OPRN = 1’b0

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0 RF_ADDR_W = 1’b0 RF_DATA_W = 1’b0

caso (estado)

`PROC_FETCH: começar

next_state = `PROC_DECODE

MEM_READ = 1’b1

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0

RF_ADDR_W = 1’b1

fim

`PROC_DECODE: começar

next_state = `PROC_EXE

MEM_ADDR = 1’b1

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

MEM_WRITE = 1’b1

RF_ADDR_R1 = 1’b1 RF_ADDR_R2 = 1’b1

fim

`PROC_EXE: começar

next_state = `PROC_MEM

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

RF_ADDR_R1 = 1’b0

fim

`PROC_MEM: começar

next_state = `PROC_WB

MEM_READ = 1’b1 MEM_WRITE = 1’b0

fim

`PROC_WB: começar

next_state = `PROC_FETCH

MEM_READ = 1’b1 MEM_WRITE = 1’b0

fim

endcase

fim

módulo final

módulo PROC_SM (STATE, CLK, RST)

// lista de entradas

entrada CLK, RST

// lista de saídas

saída [2: 0] ESTADO

// lista de entrada

entrada CLK, RST

// lista de saída

saída ESTADO

reg [2: 0] ESTADO

estado reg [1: 0]

reg [1: 0] next_state

reg PC_REG, INST_REG, SP_REF

`definir PROC_FETCH 3’h0

`define PROC_DECODE 3’h1

`definir PROC_EXE 3’h2

`definir PROC_MEM 3’h3

`define PROC_WB 3’h4

// iniciação do estado

inicial

começar

estado = 2’bxx

next_state = `PROC_FETCH

fim

// redefine o tratamento do sinal

sempre @ (posedge RST)

começar

estado = `PROC_FETCH

next_state = `PROC_FETCH

fim

sempre @ (posedge CLK)

começar

state = next_state

fim

sempre @ (estado)

começar

if (estado === `PROC_FETCH)

começar

next_state = `PROC_DECODE

print_instruction (INST_REG)

fim

if (estado === `PROC_DECODE)

começar

next_state = `PROC_EXE

fim

if (estado === `PROC_EXE)

começar

next_state = `PROC_MEM

print_instruction (SP_REF)

fim

if (estado === `PROC_MEM)

começar

next_state = `PROC_WB

fim

if (estado === `PROC_WB)

começar

next_state = `PROC_FETCH

print_instruction (PC_REG)

fim

fim

tarefa print_instruction

entrada [`DATA_INDEX_LIMIT: 0] inst

código de operação reg [5: 0]

reg [4: 0] rs

reg [4: 0] rt

reg [4: 0] rd

reg [4: 0] shamt reg [5: 0] funct reg [15: 0] endereço reg imediato [25: 0]

começar

// analisa a instrução

// tipo R

{opcode, rs, rt, rd, shamt, funct} = inst

// Eu digito

{opcode, rs, rt, imediato} = inst

// tipo J

{opcode, endereço} = inst

$ write (“@% 6dns -> [0X% 08h]“, $ time, inst)

case (opcode) // R-Type

6h00: início

case (função)

6’h20: $ write (“add r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6’h22: $ write (“sub r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6’h2c: $ write (“mul r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6’h24: $ write (“e r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6’h25: $ write (“ou r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6’h27: $ write (“nor r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6’h2a: $ write (“slt r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6’h00: $ write (“sll r [% 02d],% 2d, r [% 02d]”, rs, shamt, rd)

6’h02: $ write (“srl r [% 02d], 0X% 02h, r [% 02d]”, rs, shamt, rd)

6’h08: $ write (“jr r [% 02d]”, rs)

padrão: $ write (“”)

endcase

fim

// Eu digito

6’h08: $ write (“addi r [% 02d], r [% 02d], 0X% 04h”, rs, rt, imediato)

6’h1d: $ write (“muli r [% 02d], r [% 02d], 0X% 04h”, rs, rt, imediato)

6’h0c: $ write (“andi r [% 02d], r [% 02d], 0X% 04h”, rs, rt, imediato)

6’h0d: $ write (“ori r [% 02d], r [% 02d], 0X% 04h”, rs, rt, imediato)

6’h0f: $ write (“lui r [% 02d], 0X% 04h”, rt, imediato)

6’h0a: $ write (“slti r [% 02d], r [% 02d], 0X% 04h”, rs, rt, imediato)

6’h04: $ write (“beq r [% 02d], r [% 02d], 0X% 04h”, rs, rt, imediato)

6’h05: $ write (“bne r [% 02d], r [% 02d], 0X% 04h”, rs, rt, imediato)

6’h23: $ write (“lw r [% 02d], r [% 02d], 0X% 04h”, rs, rt, imediato)

6’h2b: $ write (“sw r [% 02d], r [% 02d], 0X% 04h”, rs, rt, imediato)

// J-Type

6’h02: $ write (“jmp 0X% 07h”, endereço)

6’h03: $ write (“jal 0X% 07h”, endereço)

6’h1b: $ write (“push”)

6’h1c: $ write (“pop”)

padrão: $ write (“”)

endcase

$ write (“ n”)

fim

finalizar tarefa

módulo final

FAQs

1). Qual é o trabalho de uma unidade de controle?

O trabalho da unidade de controle é direcionar o fluxo de dados ou instruções para a execução pelo processador de um computador. Ele controla, gerencia e coordena a memória principal, ALU, registros, unidades de entrada e saída. Ele busca as instruções e gera sinais de controle para a execução.

2). Qual é a memória de controle?

A memória de controle geralmente é RAM ou ROM para armazenar o endereço e os dados do registro de controle.

3). O que é a unidade de controle Wilkes?

O sequencial e circuitos combinacionais da unidade de controle com fio são substituídos pela unidade de controle Wilkes. Ele usa uma unidade de armazenamento para armazenar as sequências de instruções de um micro-programa.

4). O que é uma unidade de controle com fio?

A unidade de controle com fio gera os sinais de controle mudando de um estado para outro em cada pulso de clock, sem qualquer mudança física no circuito. A geração de sinais de controle depende dos sinais de registro, decodificador e interrupção de instruções.

5). Qual é a memória de controle?

As informações da unidade de controle ou dados são temporariamente ou permanentemente armazenados na memória de controle.

A memória de controle é de dois tipos. Eles são memória de acesso aleatório (RAM) e memória somente leitura (ROM).

Portanto, trata-se de definição, componentes, design, diagrama, funções e tipos de unidade de controle . Aqui está uma pergunta para você, “Qual é a finalidade do registro de endereço de controle?”