JTAG (Joint Test Action Group) é um padrão IEEE 1149.1 bem estabelecido que foi desenvolvido no ano de 1980 para resolver os problemas de fabricação que ocorriam em placas eletrônicas ou placas de circuito impresso . Essa tecnologia é usada para fornecer acesso de teste suficiente para cada placa complexa quando o acesso de teste estava diminuindo. Assim, a tecnologia de varredura de limites foi lançada e o padrão JTAG ou Especificação JTAG é estabelecido. A complexidade da eletrônica vem aumentando dia a dia, então a especificação JTAG se tornou o formato de teste aceito para testar unidades eletrônicas complicadas e compactas. Este artigo apresenta uma visão geral de um JTAG protocolo – trabalhando com aplicativos.

O que é JTAG?

O nome que é dado à Porta de Acesso de Teste Padrão IEEE 1149.1, bem como à Arquitetura Boundary-Scan, é conhecido como JTAG (Joint Test Action Group). Essa arquitetura de varredura de limite é usada principalmente em computadores processadores porque o primeiro processador com JTAG foi lançado pela Intel. Este padrão IEEE simplesmente define como o circuito de um computador é testado para confirmar se está funcionando corretamente após o procedimento de fabricação. Nas placas de circuito, são realizados testes para verificar as juntas de solda.

O Joint Test Action Group fornece uma visualização de pinos para testadores com cada bloco de IC que ajuda a identificar quaisquer falhas dentro de uma placa de circuito. Uma vez que este protocolo é conectado a um chip, ele pode anexar uma sonda ao chip, permitindo que um desenvolvedor controle o chip, bem como suas conexões com outros chips. A interface com o grupo Joint Test Action também pode ser usada pelos Desenvolvedores para copiar o firmware para memória não volátil em um dispositivo eletrônico.

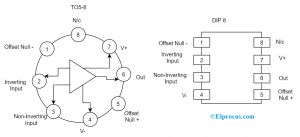

Configuração/Pinagem

O Joint Test Action Group inclui 20 pinos onde cada pino e sua função são discutidos abaixo.

Pino1 (VTref): Este é o pino de tensão de referência do alvo que é usado para conectar à fonte de alimentação principal do alvo que varia de 1,5 a 5,0 VCC.

Pin2 (V de alimentação): Esta é a tensão de alimentação alvo que é usada para conectar a alimentação de tensão principal do alvo 1,5 VCC – 5,0 VCC.

Pin3 (nTRST): Este é um pino de reset de teste que é usado para redefinir a máquina de estado do controlador TAP.

Pinos (4, 6, 8, 10, 12, 14, 16, 18 e 20): Estes são pinos GND comuns.

Pin5 (TDI): Estes são dados de teste no pino. Esses dados são transferidos para o dispositivo de destino. Este pino deve ser puxado para cima em uma condição definida na placa alvo.

Pino 7 (TMS): Este é o pino de estado do modo de teste que é puxado para determinar a próxima condição da máquina de estado do controlador TAP.

Pin9 (TCK): Este é um pino de relógio de teste que sincroniza as operações internas da máquina de estado no controlador TAP.

Pino 11 (RTCK): Este é o pino TCK de retorno de entrada usado em dispositivos que suportam clock adaptável.

Pino 13 (TDO): Este é o pino Test Data Out, então os dados são movidos para fora do dispositivo alvo para o Flyswatter.

Pin15 (nSRST): Este é o pino de reinicialização do sistema de destino que está conectado ao sinal de reinicialização principal do destino.

Pinos 17 e 19 (NC): Estes não são pinos conectados.

JTAG funcionando

O uso original do JTAG é para testes de limite. Aqui, é uma placa de circuito impresso simples, incluindo dois ICs como CPU e FPGA . Uma placa típica pode incluir muitos CIs. Em geral, os CIs incluem muitos pinos que são conectados em conjunto com muitas conexões. Aqui, no diagrama a seguir, apenas quatro conexões são mostradas.

Então, se você projetar muitas placas onde cada placa tem milhares de conexões. Nele, existem algumas placas ruins. Portanto, precisamos verificar qual placa está funcionando e qual não está funcionando. Para isso, foi criado o Grupo de Ação de Testes Conjuntos.

Este protocolo pode usar os pinos de controle de todos os chips, mas no diagrama a seguir, o Grupo de Ação de Teste Conjunto fará todos os pinos de saída da CPU e todos os pinos de entrada do FPGA. Depois disso, transmitindo uma certa quantidade de dados dos pinos da CPU e lendo os valores dos pinos do FPGA, o JTAG informa que as conexões da placa PCB estão bem.

Na verdade, o Joint Test Action Group inclui quatro sinais lógicos TDI, TDO, TMS e TCK. E esses sinais precisam ser conectados de uma maneira particular. A princípio, TMS e TCK são conectados em paralelo a todos os ICs do JTAG.

Depois disso, tanto o TDI quanto o TDO são conectados para formar uma cadeia. Como você pode observar, todo IC compatível com JTAG inclui 4 pinos que são usados para JTAG onde 3 pinos são entradas e 4 pinos são saídas. O quinto pino como TRST é opcional. Normalmente, os pinos JTAG não são compartilhados para outros fins.

Ao usar o Grupo de Ação de Teste Conjunto, todos os CIs utilizam testes de limite cujo motivo original é criado pelo JTAG. Atualmente, o uso deste protocolo foi estendido para permitir coisas diferentes, como configurar FPGAs e depois disso, JTAG é usado no núcleo do FPGA para fins de depuração.

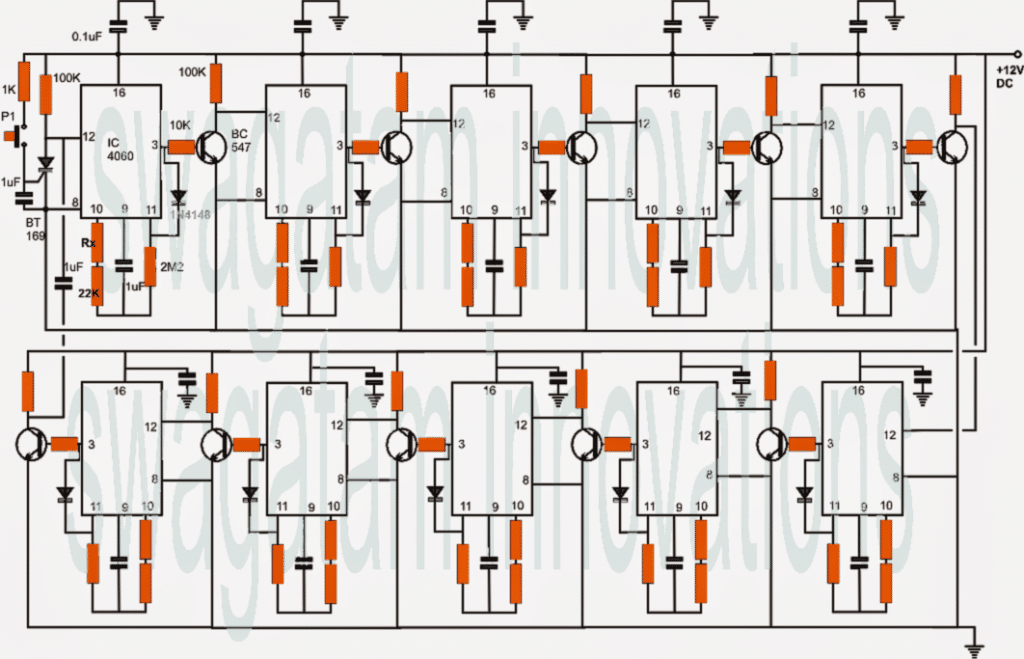

Arquitetura JTAG

A arquitetura JTAG é mostrada abaixo. Nesta arquitetura, todos os sinais entre a lógica central do dispositivo e os pinos são interrompidos através de um caminho de varredura serial chamado BSR ou Boundary Scan Register. Este BSR inclui várias “células” de varredura de limite. Geralmente, essas células de varredura de limite não são visíveis, mas podem ser usadas para definir ou ler valores no modo de teste dos pinos do dispositivo.

A interface JTAG chamada de TAP ou Porta de Acesso de Teste usa sinais diferentes para suportar a operação de varredura de limite como TCK, TMS, TDI, TDO e TRST.

- O sinal TCK ou Test Clock simplesmente sincroniza as operações internas de uma máquina de estado.

- O sinal TMS ou Test Mode Select é amostrado na borda crescente de um sinal de clock de teste para decidir o próximo estado.

- TDI ou sinal de entrada de dados de teste significa que os dados foram transferidos para o dispositivo de teste, caso contrário, a lógica de programação. Uma vez que a máquina de estado interna está no estado correto, ela é amostrada na borda crescente de TCK.

- TDO ou sinal de saída de dados de teste significa os dados deslocados do dispositivo de teste de outra forma lógica de programação. Uma vez que a máquina de estado interna está no estado correto, ela é válida na borda decrescente do TCK

- TRST ou Test Reset é um pino opcional que é usado para redefinir a máquina de estado do controlador TAP.

Controlador TAP

O ponto de acesso de teste na arquitetura do JTAG é composto por um controlador TAP, um registrador de instruções e registradores de dados de teste. Este controlador inclui a máquina de estado de teste que é responsável pela leitura dos sinais TMS e TCK. Aqui, o pino i/p de dados é usado simplesmente para carregar dados nas células de limite entre o núcleo do IC e os pinos físicos, e também carregar dados em um dos registradores de dados ou no registrador de instruções. O pino o/p de dados é usado para ler dados dos registradores ou das células de limite.

A máquina de estado do controlador TAP é controlada pelo TMS e é cronometrada pelo TCK. A máquina de estado usa dois caminhos para significar dois modos diferentes, como modo de instrução e modo de dados.

Registros

Existem dois tipos de registradores disponíveis na varredura de limite. Cada dispositivo compatível inclui no mínimo dois ou mais registradores de dados e um registrador de instruções.

Registro de Instrução

O registrador de instrução é usado para manter a instrução atual. Assim, seus dados são utilizados pelo controlador TAP para decidir o que executar com os sinais obtidos. Mais frequentemente, os dados do registrador de instrução descreverão para qual dos registradores de dados os sinais devem ser passados.

Registros de dados

Os registradores de dados estão disponíveis em três tipos: BSR (Boundary Scan Register), BYPASS e ID CODES. E também, outros registros de dados podem estar lá, porém eles não são necessários como elemento do padrão JTAG.

Registro de varredura de limite (BSR)

O BSR é o principal registrador de dados de teste usado para transferir dados de e para os pinos de E/S do dispositivo.

DESVIAR

Bypass é um registrador de bit único usado para passar dados de TDI – TDO. Assim, permite que dispositivos adicionais dentro de um circuito sejam testados por sobrecarga mínima.

CÓDIGOS DE IDENTIFICAÇÃO

Este tipo de registro de dados inclui o código de identificação, bem como o número de revisão do dispositivo. Portanto, esses dados permitem que o dispositivo seja conectado ao seu arquivo BSDL (Boundary Scan Description Language). Este arquivo inclui os detalhes de configuração do Boundary Scan para o dispositivo.

O funcionamento do JTAG é, inicialmente, o modo de instrução é escolhido onde um dos estados neste modo ‘caminho’ deixa o operador cronometrar dentro de uma instrução por TDI. Depois disso, a máquina de estado se desenvolve até se reorganizar. O próximo passo para a maioria das instruções é escolher o modo de dados. Portanto, neste modo, os dados são carregados através do TDI para serem lidos do TDO. Para TDI e TDO, os caminhos de dados serão organizados de acordo com a instrução que foi cronometrada. Uma vez que a operação de leitura/gravação é feita, novamente a máquina de estado desenvolve para o estado de reset.

Diferença entre JTAG e UART

A diferença entre JTAG e UART inclui o seguinte.

| JTAG |

UART |

| O termo “JTAG” significa Joint Test Action Group. | O termo ' UART ” significa Receptor/Transmissor Assíncrono Universal. |

| É uma interface síncrona que utiliza hardware embutido para programar o flash . | UART é uma interface assíncrona que utiliza um carregador de inicialização que é executado na memória. |

| É um conjunto de portas de teste que são usadas para depuração, mas também podem ser usadas para programar firmware (o que geralmente é feito).

|

UART é um tipo de chip que controla as comunicações de e para um dispositivo, como um microcontrolador, ROM, RAM, etc. Na maioria das vezes, é uma conexão serial que nos permite comunicar com um dispositivo. |

| Estes estão disponíveis em quatro tipos TDI, TDO, TCK, TMS e TRST. | Estes estão disponíveis em dois tipos burro UART e FIFO UART. |

| O Joint Test Action Group é um protocolo de programação serial ou de acesso a dados usado na interface de microcontroladores e dispositivos relacionados. | Um UART é um tipo de chip, outro subcomponente do microcontrolador, que é usado para fornecer o hardware para gerar um fluxo serial assíncrono como RS-232/RS-485. |

| Os componentes JTAG são Processadores, FPGAs, CPLDs , etc. | Os componentes UART são gerador CLK, registradores de deslocamento de E/S, buffers de transmissão ou recepção, buffer de barramento de dados do sistema, lógica de controle de leitura ou gravação, etc. |

Analisador de protocolo JTAG

JTAG Protocol Analyzer como PGY-JTAG-EX-PD é um tipo de Protocol Analyzer, incluindo alguns recursos para capturar e depurar a comunicação entre o host e o design em teste. Este tipo de analisador é o instrumento líder que permite que os engenheiros de teste e projeto testem os projetos específicos do JTAG para suas especificações, organizando o PGY-JTAG-EX-PD como Mestre ou Escravo para gerar tráfego JTAG e decodificar os pacotes de decodificação do Protocolo do Grupo de Ação de Teste Conjunto.

Características

Os recursos do analisador de protocolo JTAG incluem o seguinte.

- Suporta até 25MH de frequências JTAG.

- Ele gera tráfego JTAG e decodificação de protocolo para o barramento simultaneamente.

- Tem capacidade mestre JTAG.

- Velocidades de dados JTAG variáveis e ciclo de trabalho.

- Atrasos TDI e TCK definidos pelo usuário.

- Interface USB 2.0 ou 3.0 do computador host.

- Análise de erros na decodificação de protocolo

- Diagrama de temporização de barramento decodificado por protocolo.

- Fluxo contínuo de dados de protocolo para o computador host para fornecer um buffer grande.

- Lista de atividades de protocolo.

- Em várias velocidades, um script de exercício pode ser escrito para combinar a geração de vários quadros de dados.

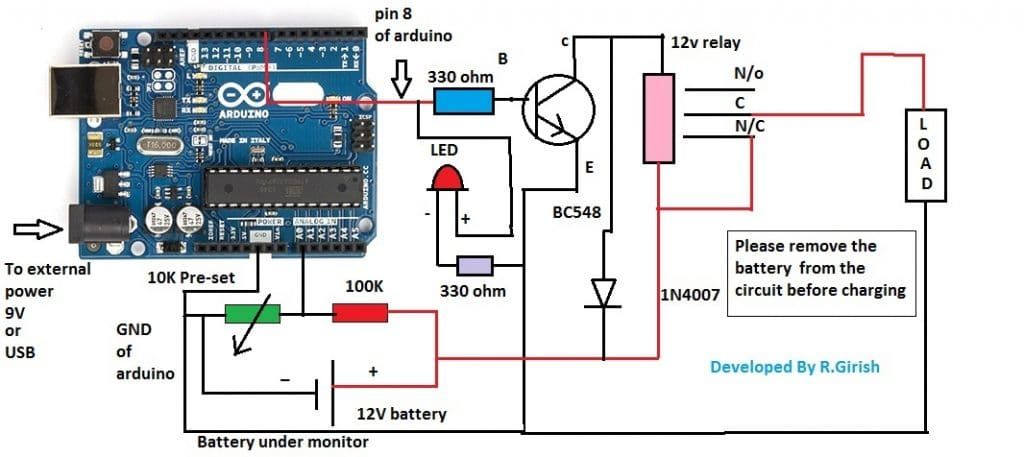

Diagrama de temporização

o diagrama de tempo do JTAG protocolo é mostrado abaixo. No diagrama a seguir, o pino TDO permanece dentro da condição de alta impedância, exceto durante um estado do controlador shift-IR/shift-DR.

Nas condições do controlador shift-IR e Shift-DR, o pino TDO é atualizado na borda decrescente do TCK através do Target e amostrado na borda crescente do TCK através do Host.

Ambos os pinos TDI e TMS são simplesmente amostrados na borda crescente do TCK através do Target. Atualizado na borda decrescente, caso contrário, TCK através do Host.

Formulários

o Aplicativos JTAG inclui o seguinte.

- O Joint Test Action Group é frequentemente usado em Processors para fornecer o direito de entrada em suas funções de emulação ou depuração.

- Todos os CPLDs e FPGAs usam isso como uma interface para dar acesso às suas funções de programação.

- É usado para testes de PCBs sem acesso físico

- É usado para testes de fabricação em nível de placa.

Assim, trata-se de tudo uma visão geral do JTAG – configuração de pinos, trabalhando com aplicativos. O padrão da indústria JTAG é usado para verificação de projeto, bem como teste de PCB após a fabricação. Aqui está uma pergunta para você, JTAG significa?

![Circuito Indicador de Pressão Atmosférica [Circuito Barômetro LED]](https://electronics.jf-parede.pt/img/3-phase-power/40/atmospheric-pressure-indicator-circuit-led-barometer-circuit-1.jpg)