A função principal do gerador de paridade e do verificador de paridade é detectar erros na transmissão de dados e este conceito foi introduzido em 1922. Na tecnologia RAID, o bit de paridade e o verificador de paridade são usados para proteger contra perda de dados. O bit de paridade é um bit extra que é definido no lado da transmissão para '0' ou '1', é usado para detectar apenas um único erro de bit e é o método mais fácil para detectar erros. Existem diferentes tipos de códigos de detecção de erros usados para detectar os erros: paridade, contador de anel, código de paridade de bloco, código de Hamming, biquinário, etc. A breve explicação sobre bit de paridade, paridade gerador e verificador são explicados abaixo.

O que é bit de paridade?

Definição: O bit de paridade ou bit de verificação são os bits adicionados ao código binário para verificar se o código particular está em paridade ou não, por exemplo, se o código está em paridade par ou a paridade ímpar é verificada por este bit de verificação ou bit de paridade. A paridade nada mais é do que o número de 1 e existem dois tipos de bits de paridade, eles são pares e ímpares.

No bit de paridade ímpar, o código deve estar em um número ímpar de 1's, por exemplo, estamos tomando o código de 5 bits 100011, este código é considerado paridade ímpar porque há três números de 1's no código que tomamos . No bit de paridade par, o código deve estar no número par de 1s, por exemplo, estamos pegando o código de 6 bits 101101, esse código é considerado paridade par porque há quatro números de 1s no código que tomamos

O que é o gerador de paridade?

Definição: O gerador de paridade é um circuito de combinação no transmissor, ele pega uma mensagem original como entrada e gera o bit de paridade para essa mensagem e o transmissor neste gerador transmite mensagens junto com seu bit de paridade.

Tipos de gerador de paridade

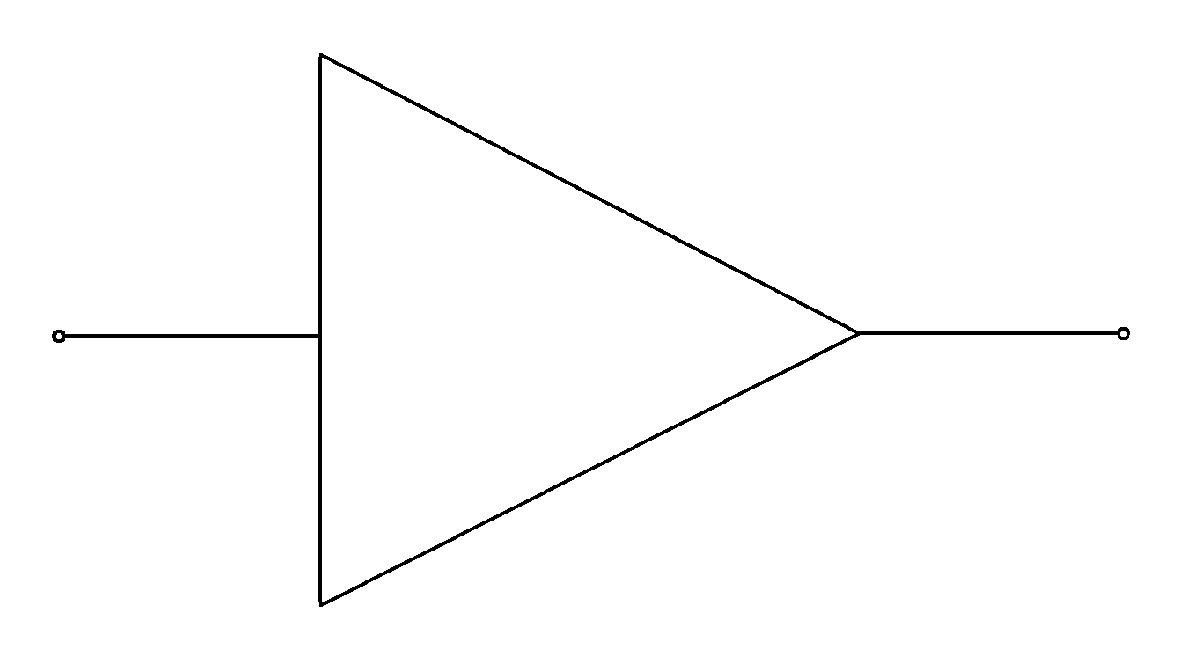

A classificação deste gerador é mostrada na figura abaixo

tipo-de-paridade-gerador

Even Parity Generator

O gerador de paridade par mantém os dados binários em número par de 1, por exemplo, os dados tomados estão em número ímpar de 1, este gerador de paridade par vai manter os dados como número par de 1 adicionando o 1 extra ao ímpar número de 1's. Este também é um circuito combinacional cuja saída depende dos dados de entrada fornecidos, o que significa que os dados de entrada são dados binários ou código binário fornecido para gerador de paridade.

Vamos considerar três dados binários de entrada, em que três bits são considerados A, B e C. Podemos escrever 23combinações usando os três dados binários de entrada que vão de 000 a 111 (0 a 7), o total de oito combinações será obtido a partir dos três dados binários de entrada que consideramos. A tabela verdade do gerador de paridade par para três dados binários de entrada é mostrada abaixo.

0 0 0 - Neste código binário de entrada, a paridade par é considerada '0' porque a entrada já está em paridade par, então não há necessidade de adicionar a paridade par mais uma vez para esta entrada.

0 0 1 - - Neste código binário de entrada, há apenas um único número de '1' e esse único número de '1' é um número ímpar de '1'. Se um número ímpar de '1' estiver lá, então o gerador de paridade par deve gerar outro '1' para torná-lo paridade par, então a paridade par é considerada como 1 para tornar o código 0 0 1 em paridade par.

0 1 0 - Este bit está em paridade ímpar, então a paridade par é considerada 1 para tornar o código 0 1 0 em paridade par.

0 1 1 - Este bit já está em paridade par, então a paridade par é considerada 0 para tornar o código 0 1 1 em paridade par.

1 0 0 - Este bit está em paridade ímpar, então a paridade par é considerada 1 para transformar o código 1 0 0 em paridade par.

1 0 1 - Este bit já está em paridade par, então a paridade par é considerada 0 para tornar o código 1 0 1 em paridade par.

1 1 0 - Este bit também está em paridade par, então a paridade par é considerada 0 para tornar o código 1 1 0 em paridade par.

1 1 1 - Este bit está em paridade ímpar, portanto a paridade par é considerada 1 para tornar o código 1 1 1 em paridade par.

Even Parity Generator Truth Table

| A B C | Paridade par |

| 0 0 0 | 0 |

| 0 0 1 | 1 |

| 0 1 0 | 1 |

| 0 1 1 | 0 |

| 1 0 0 | 1 |

| 1 0 1 | 0 |

| 1 1 0 | 0 |

| 1 1 1 | 1 |

A simplificação do mapa de karnaugh (k-map) para a paridade par de entrada de três bits é

k-map-for-even-parity-generator

A partir da tabela verdade de paridade par acima, a expressão simplificada do bit de paridade é escrita como

A expressão de paridade par implementada usando duas portas Ex-OR e o diagrama lógico desta paridade par usando o Ex-OR porta lógica é mostrado abaixo.

circuito lógico de paridade par

Desta forma, o gerador de paridade par gera um número par de 1s tomando os dados de entrada.

Gerador de paridade ímpar

O gerador de paridade ímpar mantém os dados binários em um número ímpar de 1, por exemplo, os dados obtidos estão em número par de 1, este gerador de paridade ímpar irá manter os dados como um número ímpar de 1 adicionando o 1 extra a o número par de 1's. Este é o circuito combinacional cuja saída é sempre dependente dos dados de entrada fornecidos. Se houver um número par de 1, apenas o bit de paridade é adicionado para transformar o código binário em um número ímpar de 1.

Vamos considerar três dados binários de entrada, em que três bits são considerados A, B e C. A tabela verdade do gerador de paridade ímpar para três dados binários de entrada é mostrada abaixo.

0 0 0 - Neste código binário de entrada, a paridade ímpar é considerada '1' porque a entrada está em paridade par.

0 0 1 - Esta entrada binária já está em paridade ímpar, então a paridade ímpar é considerada como 0.

0 1 0 - Esta entrada binária também está em paridade ímpar, então a paridade ímpar é considerada 0.

0 1 1 - Este bit está em paridade par, então a paridade ímpar é considerada 1 para tornar o código 0 1 1 em paridade ímpar.

1 0 0 - Este bit já está em paridade ímpar, então a paridade ímpar é considerada 0 para tornar o código 1 0 0 em paridade ímpar.

1 0 1 - Este bit de entrada está em paridade par, então a paridade ímpar é considerada 1 para tornar o código 1 0 1 em paridade ímpar.

1 1 0 - Este bit está em paridade par, então a paridade ímpar é considerada 1.

1 1 1 - Este bit de entrada está em paridade ímpar, então a paridade ímpar é considerada o.

Tabela de verdade do gerador de paridade ímpar

| A B C | Paridade ímpar |

| 0 0 0 | 1 |

| 0 0 1 | 0 |

| 0 1 0 | 0 |

| 0 1 1 | 1 |

| 1 0 0 | 0 |

| 1 0 1 | 1 |

| 1 1 0 | 1 |

| 1 1 1 | 0 |

A simplificação do mapa Kavanaugh (k-map) para a paridade ímpar de entrada de três bits é

k-map-for-odd-parity-generator

A partir da tabela verdade de paridade ímpar acima, a expressão simplificada do bit de paridade é escrita como

O diagrama lógico deste gerador de paridade ímpar é mostrado abaixo.

circuito lógico

Desta forma, o gerador de paridade ímpar gera um número ímpar de 1s, pegando os dados de entrada.

O que é a verificação de paridade?

Definição: O circuito combinacional no receptor é o verificador de paridade. Este verificador leva a mensagem recebida incluindo o bit de paridade como entrada. Ele dá saída '1' se houver algum erro encontrado e dá saída '0' se nenhum erro for encontrado na mensagem incluindo o bit de paridade.

Tipos de verificador de paridade

A classificação do verificador de paridade é mostrada na figura abaixo

verificador de tipos de paridade

Even Parity Checker

No verificador de paridade par, se o bit de erro (E) for igual a ‘1’, então temos um erro. Se o bit de erro E = 0, indica que não há erro.

Bit de erro (E) = 1, ocorre erro

Bit de erro (E) = 0, sem erro

O circuito verificador de paridade é mostrado na figura abaixo

circuito lógico

Verificador de paridade ímpar

No verificador de paridade ímpar, se um bit de erro (E) for igual a '1', então indica que não há erro. Se um bit de erro E = 0, indica que há um erro.

Bit de erro (E) = 1, sem erro

Bit de erro (E) = 0, ocorre erro

O verificador de paridade não será capaz de detectar se há erros em mais de ‘1’ bit e a correção dos dados também não é possível, essas são as principais desvantagens do verificador de paridade.

Gerador / verificador de paridade usando ICs

O IC 74180 desempenha a função de geração de paridade e também de verificação. O Gerador / Verificador de Paridade de 9 bits (8 bits de dados, 1 bit de paridade) é mostrado na figura abaixo.

ic-74180

O IC 74180 contém oito bits de dados (X0para X7), VDC,entrada par, entrada ímpar, saída Seven, saída S ímpar e pino de aterramento.

Se as entradas pares e ímpares fornecidas forem altas (H), então as saídas pares e ímpares serão baixas (L), da mesma forma, se as entradas fornecidas forem baixas (L), então as saídas pares e ímpares se tornarão altas ( H).

Vantagens da Paridade

As vantagens da paridade são

- Simplicidade

- Fácil de usar

Formulários de paridade

As aplicações de paridade são

- No sistemas digitais e muitos aplicativos de hardware, esta paridade é usada

- O bit de paridade também é usado em Small Computer System Interface (SCSI) e também em Peripheral Component Interconnect (PCI) para detectar os erros

FAQs

1). Qual é a diferença entre o gerador de paridade e o verificador de paridade?

O gerador de paridade gera o bit de paridade no transmissor e o verificador de paridade verifica o bit de paridade no receptor.

2). O que significa sem paridade?

Quando os bits de paridade não são usados para verificar erros, o bit de paridade é considerado sem paridade, sem paridade ou ausência de paridade.

3). Qual é o valor de paridade?

O conceito de valor de paridade usado para commodities e títulos e o termo se refere a quando o valor dos dois ativos é igual.

4). Por que precisamos de um verificador de paridade?

O verificador de paridade é necessário para detectar os erros na comunicação e também no verificador de paridade dos dispositivos de armazenamento de memória é usado para teste.

5). Como o bit de paridade pode detectar uma unidade de dados danificada?

O bit redundante nesta técnica é chamado de bit de paridade, ele detecta a unidade de dados danificada quando ocorre um erro durante a transmissão de dados.

Neste artigo, como o paridade gerador e verificador geram e verificam o bit e seus tipos, circuitos lógicos, tabelas verdade e expressões k-map são discutidos brevemente. Aqui está uma pergunta para você, como você calcula a paridade par e ímpar?