O processo de design de hardware digital mudou intensamente nos últimos anos. Portanto, pequenos circuitos digitais podem ser implementados usando PALs e PLAs. Cada dispositivo é usado para implementar vários circuitos que não precisam de mais do que o número de i / ps, o / ps e termos de produto que são oferecidos no chip específico. Esses chips são inadequados para tamanhos bastante modestos, normalmente suportando um número mútuo de entradas e saídas não superior a 32. Para projetar esses circuitos que precisam de mais entradas e saídas, numerosos PLAs / PALs podem ser empregados ou então um tipo mais elegante do chip pode ser usado denominado CPLD (dispositivo lógico programável complexo). Um chip CPLD inclui vários blocos de circuito em um único chip com recursos de fiação internos para conectar os blocos de circuito. Cada bloco de circuito é comparável a um PLA ou PAL.

O que é um dispositivo lógico programável complexo?

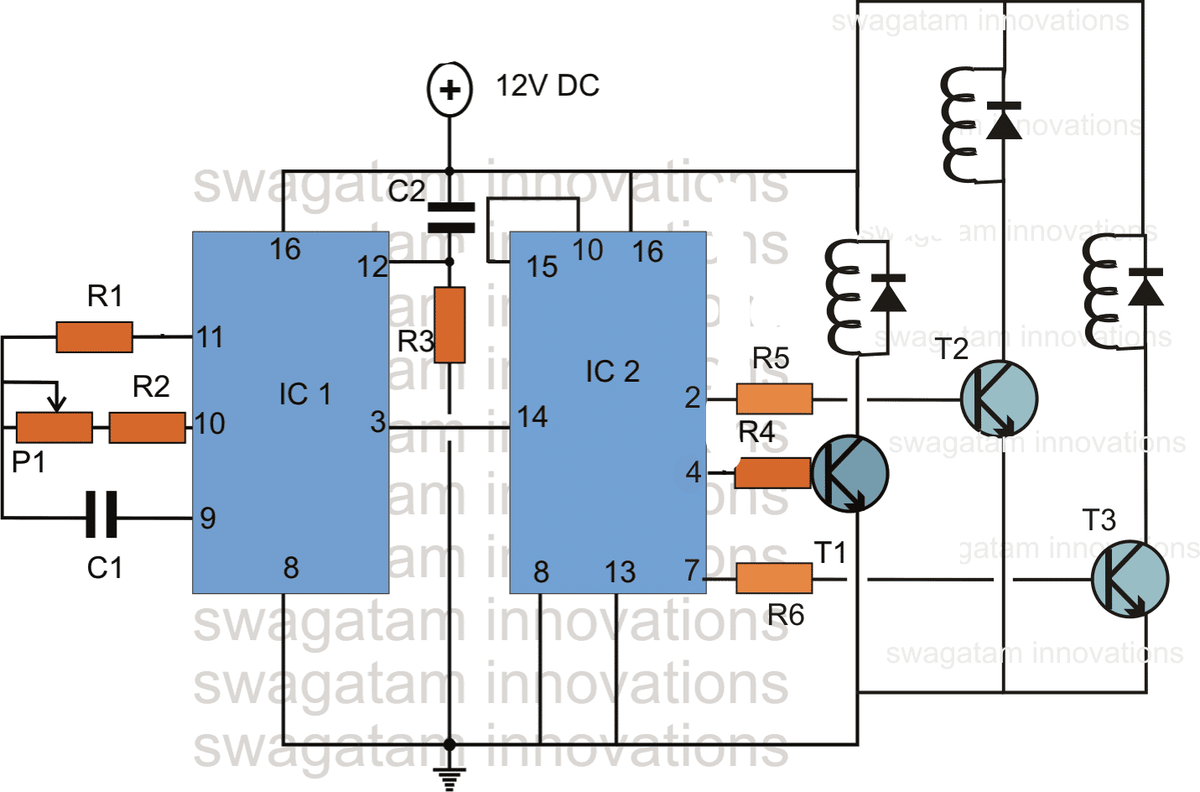

A sigla do CPLD é 'Dispositivos lógicos programáveis complexos', é um tipo de circuito integrado que os designers de aplicativos desenvolvem para implementar hardware digital como telefones celulares. Estes podem lidar com projetos conscientemente maiores do que SPLDs (dispositivos lógicos programáveis simples), mas oferecem menos lógica do que FPGAs ( matrizes de portas programáveis em campo ) .CPLDs incluem vários blocos lógicos, cada um dos blocos inclui 8-16 macrocélulas. Como cada bloco lógico executa uma função específica, todas as macrocélulas em um bloco lógico estão totalmente conectadas. Dependendo do uso, esses blocos podem ou não ser conectados uns aos outros.

Dispositivo lógico programável complexo

A maioria dos CPLDs (dispositivos lógicos programáveis complexos) têm macrocélulas com uma soma de função lógica e um eletivo FF (flip-flop) . Dependendo do chip, a função lógica combinatória suporta de 4 a 16 termos de produto com fan-in inclusivo. Os CPLDs também diferem em termos de registros de deslocamento e portas lógicas. Por esta razão, CPLDs com um grande número de portas lógicas podem ser usados no lugar de FPGAs. Outra especificação CPLD significa o número de termos do produto que uma macrocélula pode cumprir. Os termos do produto são o produto de sinais digitais que executam uma função lógica específica.

Os CPLDs estão disponíveis em vários formatos de pacote IC e famílias lógicas. Os CPLDs também diferem em termos de tensão de alimentação, corrente operacional, corrente de espera e dissipação de energia. Além disso, eles podem ser obtidos com várias quantidades de memória e vários tipos de suporte de memória. Normalmente, a memória é expressa em bits / megabits. O suporte de memória consiste em ROM, RAM e RAM de porta dupla. Ele também compreende CAM (memória endereçável de conteúdo), bem como memória FIFO (primeiro a entrar, primeiro a sair) e memória LIFO (último a entrar, último a sair).

Arquitetura de dispositivo lógico programável complexo

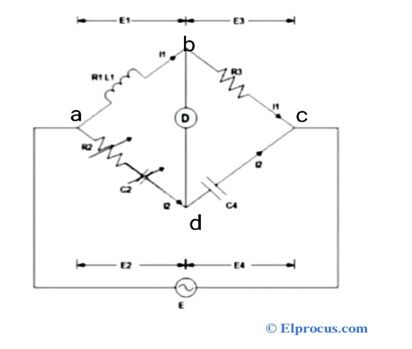

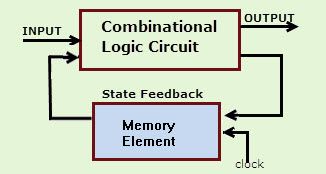

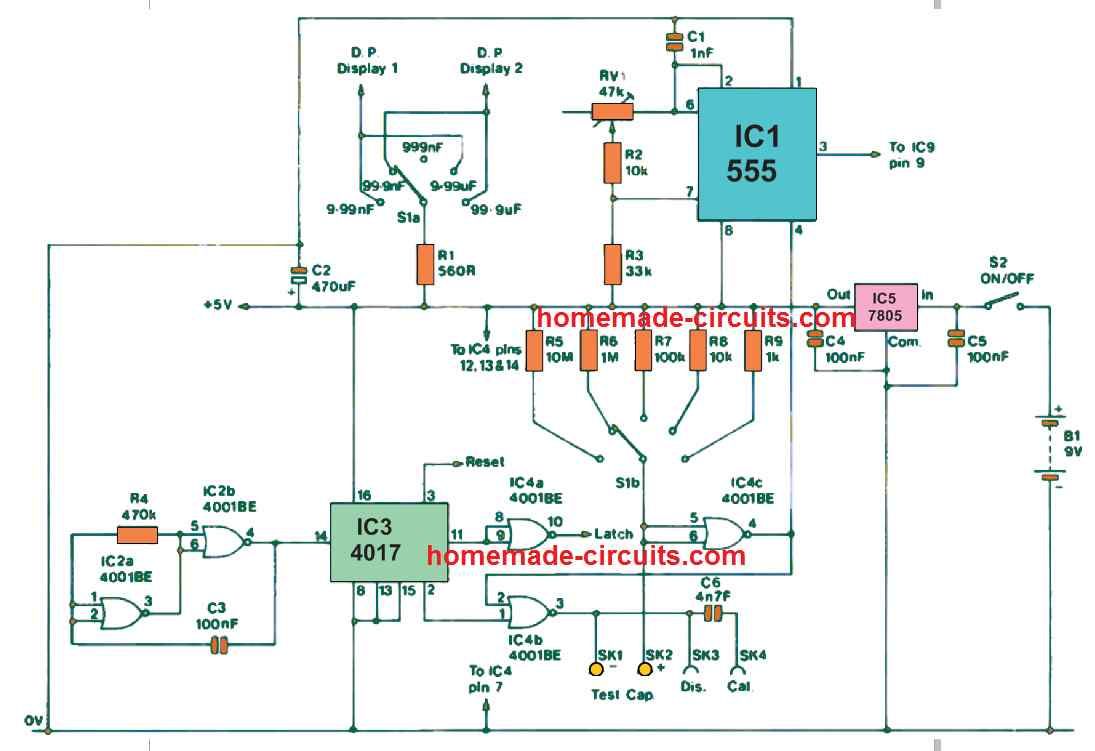

Um dispositivo lógico programável complexo é composto por um grupo de FBs programáveis (blocos funcionais). As entradas e saídas desses blocos funcionais são conectadas por um GIM (matriz de interconexão global). Esta matriz de interconexão é reconfigurável, para que possamos modificar os contatos entre os blocos funcionais. Haverá alguns blocos de entrada e saída que nos permitirão unir o CPLD ao mundo externo. A arquitetura do CPLD é mostrada abaixo.

Geralmente, o FB programável se parece com o matriz de portas lógicas , onde uma matriz de portas AND pode ser programada e as portas OR são estáveis. Mas, cada fabricante tem sua maneira de pensar para projetar o bloco funcional. Um o / p listado pode ser encontrado operando os sinais de feedback obtidos nas saídas da porta OR.

Arquitetura CPLD

Na programação CPLD, o design é primeiro codificado em linguagem Verilog ou VHDL assim que o código é (simulado e sintetizado. Durante a síntese, o modelo CPLD (dispositivo de destino) é escolhido manualmente e uma lista de rede de mapeamento baseada em tecnologia é produzida. Esta lista pode ser fechada - ajustar à arquitetura CPLD genuína usando um processo de localização e rota, normalmente obtido pelo software de localização e rota de propriedade da empresa de CPLD. Em seguida, o operador fará alguns processos de confirmação. Se tudo estiver bem, ele utilizará o CPLD, caso contrário ele vai reorganizá-lo.

Problemas de arquitetura do CPLD

Ao considerar um dispositivo lógico programável complexo para uso no projeto, alguns problemas de arquitetura a seguir podem ser levados em consideração

- A tecnologia de programação

- A capacidade do bloco de funções

- A capacidade de I / O

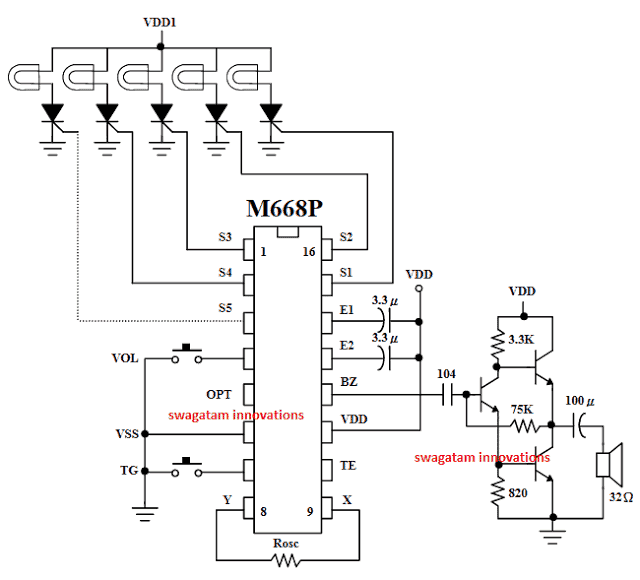

Algumas das famílias de CPLD de diferentes varejistas incluem

- Famílias Altera MAX 7000 e MAX 9000

- Famílias Atmel ATF e ATV

- Família Lattice isp LSI

- Lattice (Vantis) família MACH

- Família Xilinx XC9500

Famílias de CPLD

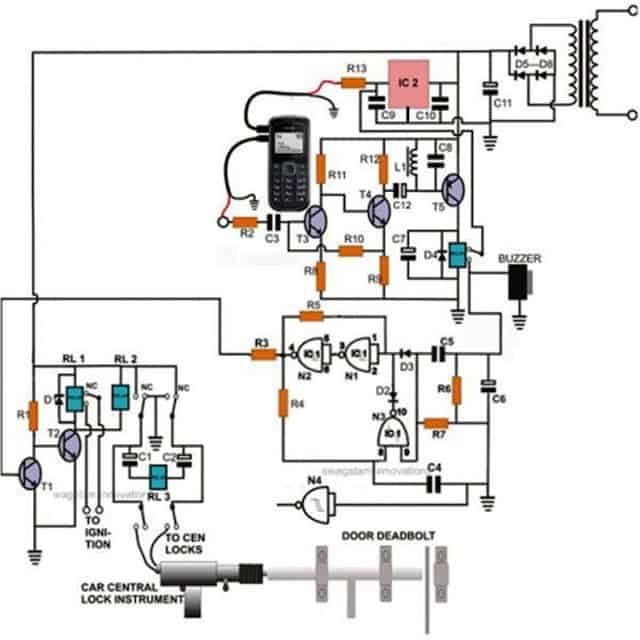

Aplicações de CPLD

As aplicações de CPLDs incluem o seguinte

- Dispositivos lógicos programáveis complexos são ideais para aplicações de controle críticas de alto desempenho.

- CPLD pode ser usado em projetos digitais para executar as funções do carregador de boot

- CPLD é usado para carregar os dados de configuração de uma matriz de portas programáveis em campo a partir da memória não volátil.

- Geralmente, eles são usados em pequenos aplicativos de design, como decodificação de endereço

- Os CPLDs são frequentemente usados em muitas aplicações, como em dispositivos portáteis operados por bateria, sensíveis ao custo, devido ao seu tamanho reduzido e uso de baixa energia.

Portanto, trata-se de uma arquitetura complexa de dispositivos lógicos programáveis e suas aplicações. Esperamos que você tenha entendido melhor este conceito. Além disso, quaisquer dúvidas sobre este conceito ou para implementar quaisquer projetos elétricos e eletrônicos , dê suas sugestões valiosas comentando na seção de comentários abaixo. Aqui está uma pergunta para você, qual é a diferença entre CPLD e FPGA?

Créditos fotográficos:

- CPLD wikimedia

- Arquitetura de CPLD slidesharecdn