O processador MicroBlaze foi desenvolvido em 2002 para integrar vários recursos complicados para atender a novas e crescentes demandas do mercado. Assim, o processador MicroBlaze é um elemento essencial dentro do portfólio Low-End da Xilinx para permitir o desenvolvimento mais rápido do sistema que contém Artix®-7 FPGAs , Spartan®-6, Zynq®-7000 AP SoCs. Este processador é extremamente configurável, portanto, pode ser usado como processador embutido ou microcontrolador dentro de FPGAs e também usado como coprocessador nos SoCs Zynq-7000 AP baseados em ARM Cortex-A9. Este artigo fornece informações breves sobre Processador MicroBlaze – arquitetura e trabalho com aplicativos.

O que é o processador Microblaze?

O microprocessador soft que é projetado principalmente para FPGAs da Xilinx é conhecido como processador MicroBlaze. Este processador é simplesmente implementado dentro da estrutura lógica e de memória de uso geral dos FPGAs da Xilinx. Este processador é semelhante à arquitetura DLX baseada em RISC e possui um sistema de interconexão flexível para suportar diferentes aplicações embarcadas. O barramento de E/S principal e a interconexão AXI do MicroBlaze é um barramento de transações mapeado na memória com um recurso mestre-escravo.

O MicroBlaze utiliza um barramento LMB dedicado para acessar a memória local e fornece armazenamento rápido no chip. Muitas partes deste processador podem ser configuradas pelo usuário, como o tamanho do cache, a profundidade da unidade de gerenciamento de memória do pipeline, periféricos incorporados e interfaces de barramento.

Recursos do Microblaze

o Características do Microblaz e incluem o seguinte. Possui 32 registradores de uso geral.

- Possui palavras de instrução de 32 bits, incluindo 2 modos de endereçamento e 3 operandos.

- O barramento de endereços é de 32 bits.

- Tem pipeline de 3 estágios ou um pipeline de 5 estágios.

- Uma unidade de bloco ALU com um shifter.

- A arquitetura Harvard inclui dados de 32 bits e barramento de endereços.

- Interface de dados e instrução de barramento de memória local ou LMB.

- Interfaces de fluxo AX14 e AX14.

- Unidade de ponto flutuante e unidade de gerenciamento de memória.

- Ele suporta lockstep.

- Interface de depuração e rastreamento.

Arquitetura Microbaze

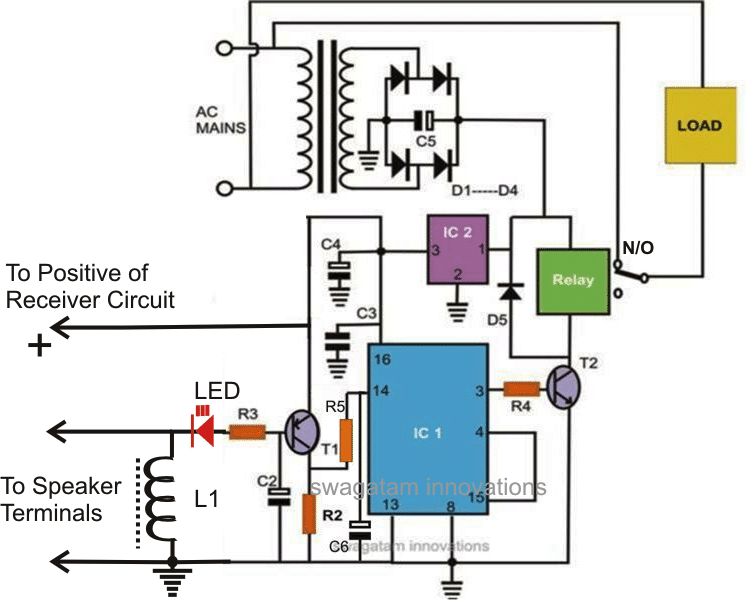

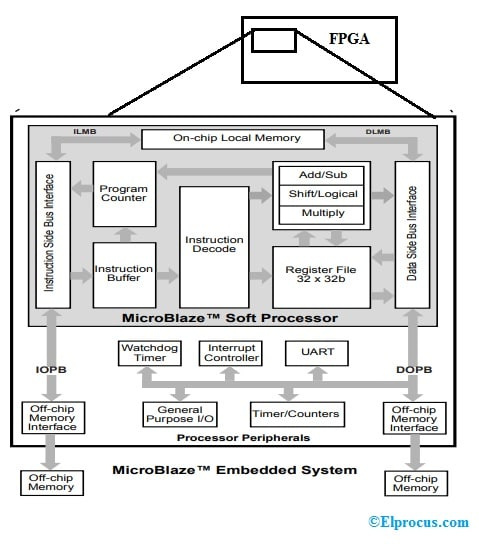

O diagrama de blocos do processador MicroBlaze é mostrado abaixo. Este processador MicroBlaze é extremamente personalizável e suporta mais de 70 opções de design. Esta arquitetura mostra recursos de hardware permanentes, bem como opções configuráveis como o Cache de Instrução ou Dados, a Unidade de Gerenciamento de Memória, a Unidade de Ponto Flutuante, etc.

Um sistema embarcado montado em torno de um processador MicroBlaze inclui principalmente MicroBlaze Soft Processor Core, On-chip Local Memory, Standard Bus Interconnects e OPB Peripherals (On-chip Peripheral Bus). Um sistema de processador MicroBlaze varia principalmente de um núcleo de processador por uma memória local a um grande sistema, incluindo vários MicroBlaze processadores , memória externa e muitos periféricos OPB.

Núcleo do processador macio

O núcleo do processador soft do MicroBlaze é central para o sistema embarcado MicroBlaze. Este é um processador RISC de 32 bits muito rápido e eficiente que possui os seguintes recursos.

- O conjunto de instruções é ortogonal.

- Barramentos separados de dados e instruções.

- registradores de uso geral de 32 bits.

- Tem um shifter barril de 32 bits completo opcional.

- Interfaces integradas para OCM rápido ou memória no chip e OPB (On-chip Peripheral Bus) padrão da indústria da IBM.

Implementações no Virtex-II e dispositivos posteriores suportam a multiplicação de hardware.

Memória local no chip

A memória síncrona é uma memória local que é usada principalmente para permitir Block RAM no chip.

Interconexões de ônibus padrão

As interfaces de barramento no lado da instrução e dos dados incluem uma interface para a memória local que é chamada de LMB (Local Memory Bus) e uma interface para o On-chip Peripheral Bus da IBM. Assim, podemos projetar sistemas que seguem estritamente a arquitetura de Harvard, caso contrário, para compartilhar recursos, podemos utilizar um único OPB em combinação por meio de um árbitro de barramento.

O barramento de memória local garante entrada de ciclo único para RAM de bloco no chip. Este é um protocolo de barramento de mestre único muito eficiente, simples e é perfeito para fazer interface com memória local rápida. O OPB ou On-chip Peripheral Bus é um barramento multimestre amplo de 32 bits que é perfeito para unir periféricos e memória externa ao núcleo do processador MicroBlaze.

Periféricos de barramento periféricos no chip

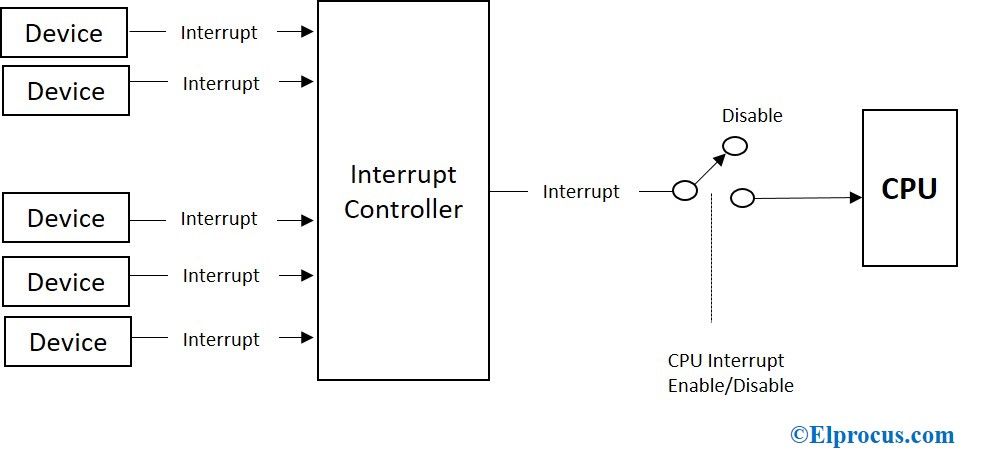

O sistema de hardware MicroBlaze é completado por periféricos OPB para fornecer diferentes funções como Watchdog Timer ou Timebase, Timer ou Contadores de uso geral, IC (Interrupt Controller), diferentes controladores como SRAM, Flash Memory, ZBT Memory, BRAM, DDR, SDRAM, UART Lite , SPI, I2C, E/S de uso geral, UART 16450/550 e Ethernet 10/100 MAC. Além disso, também podemos adicionar e definir periféricos principalmente para funções personalizadas, caso contrário, uma interface para um design que existe no FPGA.

Conjunto de instruções Microblaze

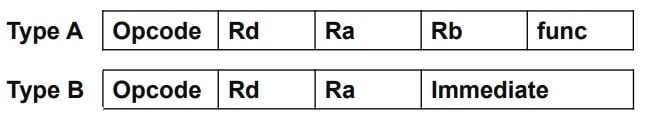

Os conjuntos de instruções Microblaze são aritmética, lógica, ramificação, carga/armazenamento e outros. O tamanho de todas as instruções é fixo. No máximo 3 registros podem ser dados como operandos. Microblaze inclui dois formatos de instrução Tipo A e Tipo B que são mostrados abaixo.

O formato de instrução do tipo A é usado principalmente para instruções de registro-registro. Portanto, inclui o opcode, destino único e dois registradores de origem. O formato de instrução tipo B é usado principalmente para instruções de registro imediato que incluem o opcode, único destino e registradores de fonte única.& uma fonte de valor imediata de 16 bits.

Nos dois formatos de instrução acima, o opcode é um código de operação, Rd é um registrador de destino que é codificado com 5 bits, Ra e Rb são registradores de origem onde cada codificado com 5 bits e Imediato é um valor de 16 bits.

Instruções aritméticas

As instruções aritméticas do tipo A e do tipo B são fornecidas abaixo.

Tipo A

|

ADICIONAR Rd, Ra, Rb adicionar |

Rd = Ra+Rb, Sinalizador de transporte afetado |

|

ADICIONE K Rd, Ra, Rb Adicionar e manter o transporte |

Rd = Ra+Rb, Sinalizador de transporte não afetado |

| RSUB Rd, Ra, Rb Subtração reversa |

Rd = R-Rb, Sinalizador de transporte não afetado |

Tipo B

|

ADICIONE I Rd, Ra, Imm adicionar imediato |

Rd = Ra+sinalExtend32 (Imm) |

|

ADICIONAR IK Rd, Ra, Imm adicione imediato e mantenha o transporte |

Rd = Ra+ sinalExtend32 (Imm) |

| RSUBIK Rd, Ra, Imm reverso subtrair com imediato |

Rd = Ra+ sinalExtend32 (Imm) -Ra |

| SRA Rd, Ra deslocamento aritmético para a direita |

Rd = (Ra>>1) |

Instruções de lógica

As instruções lógicas do tipo A e do tipo B são fornecidas abaixo.

Tipo A

|

OU Rd, Ra, Rb Lógico ou |

Rd = Ra| Rb |

|

E Rd,Ra,Rb Adição lógica |

Rd = Ra & Rb |

| XOR Rd, Ra, Rb xor lógico |

Rd = Rb ^ Rb |

| ANDN Rd, Ra, Rb Lógico e não |

Rd = Ra & (Rb) |

Tipo B

|

ORI Rd, Ra, Imm OR lógico com imediato |

Rd = Ra | signExtend32 (Imm) |

| ANDI Rd, Ra, Imm E lógico com imediato |

Rd = Ra & sinalExtend32 (Imm) |

| XORI Rd, Ra, Imm XOR logoical com imediato |

Rd = Ra ^ signExtend32 (Imm) |

| ANDNI Rd, Ra, Imm Lógico E NÃO com imediato |

Rd = Ra & (sinalExtend32 (Imm)) |

Instruções de Ramificação - Incondicional

Modificar o registro do contador de programa

| BRID Imm filial imediata com atraso imediato |

PC = PC+ sinalExtend32 (Imm) permitir execução de slot de atraso |

| BRLID Rd, Imm branch e link imediato com atraso imediato (chamada de função) |

Rd = PC PC = PC+& sinalExtend32 (Imm) permitir execução de slot de atraso |

| RTSD Ra, Imm retorno da sub-rotina |

PC = Ra + sinalExtend32 (Imm) permitir execução de slot de atraso |

| RTID Ra, Imm retorno da interrupção |

PC = Ra + sinalExtend32 (Imm) permitir execução de slot de atraso definir interrupção habilitar no MSR |

Instruções de Ramificação - Incondicional1

Altere o registro do contador de programa quando uma condição for satisfeita

| BEQI Ra, Imm ramo se igual |

PC = PC+ sinalExtend32 (Imm) Se Ra = = 0 |

| MASH Ra, Imm ramo se não for igual |

Rd = PC PC = PC+& sinalExtend32 (Imm) Se Rá! = 0 |

Instruções de Ramificação - Incondicional2

Altere o registro do contador de programa quando uma condição for satisfeita

| BLTI Ra, Imm ramo se menor que |

PC = PC+ sinalExtend32 (Imm) Se Ra < 0 |

| BLEI Ra, Imm ramo se menor for igual a |

Rd = PC PC = PC+& sinalExtend32 (Imm) Se Ra!< = 0 |

| BGTI Ra, Imm ramo se maior que |

PC = PC+ sinalExtend32 (Imm) Se Ra!> 0 |

| BGEI Ra, Imm ramo se maior igual a |

PC = PC+sinalExtend32 (Imm) Se Ra!>= 0 |

Instruções de carregamento/armazenamento - Tipo A

| LW Rd, Ra, Rb Carregar palavra |

Endereço = Ra+Rb Rd = *Endereço |

| SW Rd, Ra, Rb Palavra da loja |

Endereço – Ra+Rb *Endereço = Rd |

Tipo B

| LWI Rd, Ra, Imn Carregar palavra imediata |

Endereço = Ra + sinalExtend32 (Imm) Rd = *Endereço |

| SW Rd, Ra, Imm Armazenar palavra imediata |

Endereço = Ra + sinalExtend32 (Imm) *Endereço = Rd |

Outras instruções

| IM, IM imediato |

Estenda o Imm de uma instrução anterior do tipo B para 32 bits. |

| MFS Rd, Sa Mover do registro de propósito especial |

Rd = Sa Sa- registrador de propósito especial, operando de origem

|

| MTS Sd, Ra Mover para registro de propósito especial |

Sd = Ra Sd – registrador de propósito especial, operando de destino |

Registros

A arquitetura do processador MicroBlaze é completamente ortogonal, que inclui registradores de uso geral de 32 bits e registradores de uso especial de 32 bits, como contador de programas e registrador de status da máquina.

Arquitetura de pipeline

O MicroBlaze utiliza uma arquitetura de pipeline de 3 estágios, incluindo busca, decodificação e estágios completos. Automaticamente, o encaminhamento de dados, as ramificações e a parada do pipeline são determinados no hardware.

Carregar ou Armazenar Arquitetura

MicroBlaze suporta memória em três tamanhos de dados 8 bits (Byte), 16 bits (Halfword) e 32 bits (Word). Assim, os acessos à memória são sempre alinhados ao tamanho dos dados. Este é um processador Big-Endian que usa o endereço do endereço Big-Endian, bem como convenções de rotulagem ao acessar a memória.

Interrupções

Uma vez que uma interrupção ocorre, este processador terminará a execução atual para gerenciar a solicitação de interrupção por meio de ramificação para o endereço do vetor de interrupção e armazenar o endereço da instrução que precisa ser executada. Este processador irá interromper futuras interrupções limpando o sinalizador IE (Interrupt Enable) dentro do MSR (Machine Status Register).

Como o Microblaze funciona?

O processador MicroBlaze suporta largura de barramento de 32 bits e esse núcleo de processador é um mecanismo baseado em RISC que inclui um arquivo de registro baseado em LUT RAM de 32 bits por meio de instruções separadas para acesso à memória e aos dados.

Este processador simplesmente suporta BlockRAM no chip e memória externa. Semelhante ao IBM PowerPC; todos os periféricos utilizam o barramento CoreConnect OPB semelhante; os periféricos do processador são compatíveis com o PowerPC no Virtex-II Pro.

O processador MicroBlaze oferece total flexibilidade para escolher a combinação de memória, periféricos e recursos de interface que fornecerão o sistema preciso que você precisa em um único FPGA com menor custo.

Diferença B/W Microblaze Vs Risc-V

o diferença entre MicroBlaze e RISC v inclui o seguinte.

|

Microblaze |

Risco-V |

| É um núcleo de microprocessador macio projetado principalmente para Xilinx FPGA.

|

RISC-V é uma arquitetura de conjunto de instruções enraizada nos princípios RISC.

|

| Ele usa a arquitetura Harvard RISC. | Ele usa a arquitetura do conjunto de instruções. |

| Sua licença é proprietária (Xilinx) | Sua licença é de código aberto. |

| A profundidade do pipeline é 3 ou 5. | A profundidade da tubulação é 5. |

| Seu desempenho é de 280 DMIPs. | Seu desempenho é de 250 DMIPs. |

| Sua velocidade é de 235 MHz. | Sua velocidade é de 250 MHz. |

| Possui 1027 LUTs. | Possui 4125 LUTs. |

| A tecnologia de implementação utilizada é o Xilinx FPGA. | A implementação da tecnologia utilizada é FPGA/ASIC. |

Vantagens do Microblaze

o vantagens do MicroBlaze inclui o seguinte.

- É econômico.

- É altamente configurável.

- Seu desempenho é alto em comparação com o ARM.

- É suportado por um kit de desenvolvimento incorporado.

- É um macio microprocessador essencial.

- Para ajudá-lo a organizar rapidamente seu aplicativo, este processador inclui três configurações fixas que estão relacionadas às classes de processador conhecidas: microcontrolador, tempo real e processador de aplicativos.

Aplicativos Microblaze

o Aplicações do MicroBlaze inclui o seguinte.

- Este processador atende a muitos requisitos de aplicativos diferentes, como industrial, automotivo, médico e consumidor, etc.

- As aplicações do MicroBlaze vão desde máquinas de estado simples baseadas em software até controladores complexos usados em aplicações embarcadas ou dispositivos baseados na Internet.

- Ele é otimizado para aplicações embarcadas como controle industrial, automação de escritório e automotivo.

- O MicroBlaze é capaz de se comunicar com um grande conjunto de periféricos para caber em aplicações de médio porte.

- A natureza suave deste processador o torna personalizável para diferentes aplicações onde os designers podem trocar recursos por tamanho para atender às metas de preço e desempenho para aplicações médicas, automotivas, industriais e de segurança.

Assim, trata-se de tudo uma visão geral do Microblaze processador. Este é um núcleo de processador soft RISC programável de 32 bits com todos os recursos. Este processador atende a diferentes requisitos em diferentes áreas, como mercados de consumo, médicos, industriais, automotivos e de infraestrutura de comunicações. É extremamente configurável, então usado como processador embutido ou microcontrolador dentro de FPGAs, de outra forma como um co-processador para o ARM. Aqui está uma pergunta para você, o que é FPGA?